#### ECE 249 VLSI Design and Simulation Spring 2005

John A. Chandy

Department of Electrical and Computer Engineering

#### **Contact Info**

- Office: ITEB 437

- Phone: 860-486-5047

- Email: john.chandy@uconn.edu

- Office Hours:TuW 11:30-1

- Website: http://www.engr.uconn.edu/~chandy/ece249

# ΤA

- Janardhan Singaraju

- Office: HBL A-65

- Available for software and lab questions

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

#### Books

- "Digital Integrated Circuits", Rabaey, Chandrakasan, and Nikolic

- Suggested reference materials

- "Principles of CMOS VLSI Design", Weste and Eshragian

- "CMOS Digital Integrated Circuits", Kang and Leblebici

- "Digital Integrated Circuits", (ECE 215 notes), Ayers

### **Class Schedule**

- Lectures are in ITE 125

- No lectures during the weeks of April 13th and April 20th.

- Labs on Wednesdays will be in ITEB C25

- No lab for the first week

- Lab will be open M-F 9-5

- Evening hours may be available later in the semester

# Homework Policy

- 5 to 6 homeworks

- Due at the beginning of class on the due date

- 7 lab assignments

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# **Grading Policy**

- 35% Exams (February 22nd and April 7th)

- 10% Homework

- 20% Labs

- 35% Final project

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# Course goals

- Be able to contribute to an industry digital VLSI design project

- Become familiar with design tools (Cadence)

- Understand design flows

- Understand behavioral, structural, and physical specifications

- Can apply VLSI design practices

# Topics

- MOS Transistor Theory

- Circuit Characterization and Performance Estimation

- CMOS Logic Design

- VLSI Design Methodologies

- VLSI Subsystem Design

- Testing and Verification

# What is VLSI design?

• The process of creating an integrated circuit from specification to fabrication

# What is an integrated circuit?

A single integrated component that contains all the primary elements of an electrical circuit - transistors, wiring, resistors, etc.

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# Integrated circuit

- Small Scale Integration (SSI)

- Tens of transistors

- Medium Scale Integration (MSI)

- Hundreds of transistors

- Large Scale Integration (LSI)

- Thousands of transistors

- Very Large Scale Integration (VLSI)

- Hundred thousands of transistors

### Intel 4004

- First microprocessor

- Designed in 1971

- 2300 transistors

- ~100 KHz

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

#### Intel 80286

- Released in 1982

- 134,000 transistors

- 6-12.5 MHz

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

### Intel Pentium IV

- Released in 2000

- 42 million transistors

- .18 micron

- > 1 GHz

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

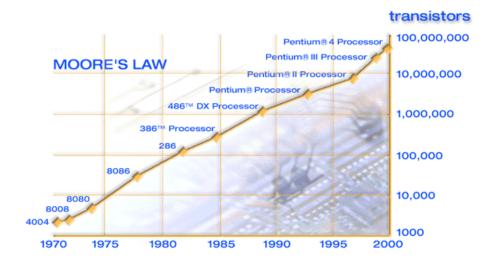

#### Moore's Law

The number of available transistors in a circuit doubles every 18 months

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# 100 million transistors???

- Partitioning

- Computer-Aided Design Tools (EDA)

- Design Methodology

- Testing and Verification

# Partitioning

- Break the problem into smaller more manageable parts

- Reuse logic modules

- Simplifies layout

- But its not always easy deciding how to partition the problem

#### Computer-Aided Design Tools

- Schematic Capture

- Synthesis

- Simulation

- Verification

- Automated placement and routing

#### Computer-Aided Design Tools

- Cadence

- Synopsys

- Mentor Graphics

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# **Design Methodology**

- Functional Specification

- What does the chip do?

- Behavioral Specification

- How does it do it? (abstractly)

- Logic Design

- How does it do it? (logically)

- Layout

- How does it do it? (physically)

# Design constraints

- Budget (\$\$\$)

- Area

- Power requirements

- Speed

- Schedule

- Risk

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

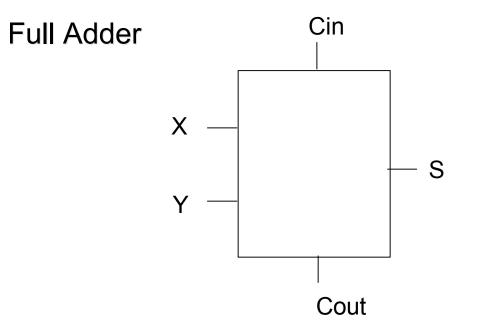

### **Functional Specification**

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# **Behavioral specification**

- VHDL

- Verilog

```

entity Full_Adder is

generic (TS : TIME := 0.11 ns; TC : TIME := .1 ns);

port (X, Y, Cin: in BIT; Cout, Sum: out BIT);

end Full_Adder

architecture Behave of Full_Adder is

begin

```

```

Sum <= X xor Y xor Cin after TS;

Cout <= (X and Y) or (X and Cin) or (Y and Cin) after TC;

end;

```

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

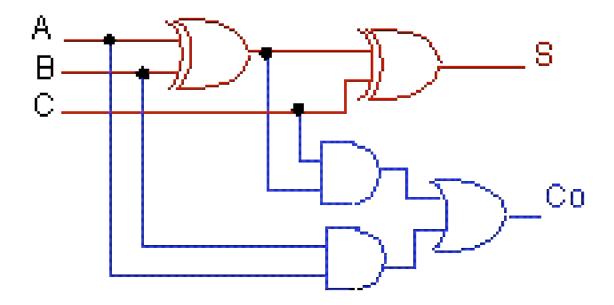

#### Logic Design

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

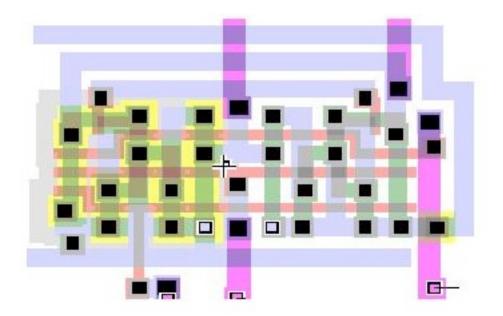

### Layout

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

#### **Testing and Verification**

- Do it at every phase of the design

- Critical to keeping to budget

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# Trust, but verify ...

| Phase              | Testing time | Time to redo | Cost to redo |

|--------------------|--------------|--------------|--------------|

| Behavioral<br>Spec | 1-2 days     | 1-2 weeks    | ~\$20K       |

| Logic Design       | 2-3 days     | 2-3 weeks    | ~\$40K       |

| Layout             | 2-3 days     | 1-2 weeks    | ~\$20K       |

| Fabrication        | 1 week       | 3-4 months   | \$1MM        |

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# VLSI Design Methodologies

- Full Custom

- Standard Cell

- Gate Array

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# Full Custom VLSI Design

- Advantages

- Fastest implementation possible

- Can be very cheap in high volumes

- Disadvantages

- Very expensive to design

- Not customizable

- Error-prone design flows

# Full Custom VLSI Alternatives

- Gate Arrays

- Advantages

- Faster than microprocessor

- Field programmable versions are easily customizable

- Design is easier than full custom VLSI

- Disadvantages

- Slower than full custom VLSI

- Limited in number of transistors/gates

- Takes more area

# Full Custom VLSI Alternatives

- Standard Cell Design

- Advantages

- Faster design time than full custom

- Higher performance than Gate Arrays

- Disadvantages

- Lower performance than full custom

- More area than full custom

# Full Custom VLSI Alternatives

- Microprocessor

- Advantages

- General purpose

- Widely available

- Cheap on a single use basis

- Design is easy

- Disadvantages

- Slower than VLSI

- Takes more area

- More expensive than VLSI over millions of units

# MOS Transistor Theory

- We will focus only CMOS VLSI design since that is the dominant design style in current industry practice

- Other VLSI technologies include:

- nMOS

- TTL

- BiCMOS

- GaAs

- ECL

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# MOS Transistor Theory

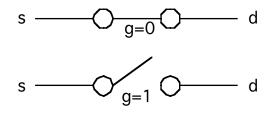

- Two types of transistors

- nMOS

- pMOS

- Digital integrated circuits use these transistors essentially as a voltage controlled switch

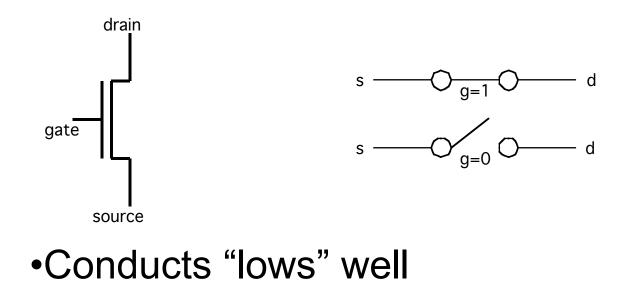

#### nMOS Transistor

# If the gate is "high", the switch is onIf the gate is "low", the switch is off

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

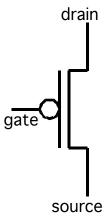

#### pMOS Transistor

# If the gate is "low", the switch is onIf the gate is "high", the switch is off

#### •Conducts "highs" well

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

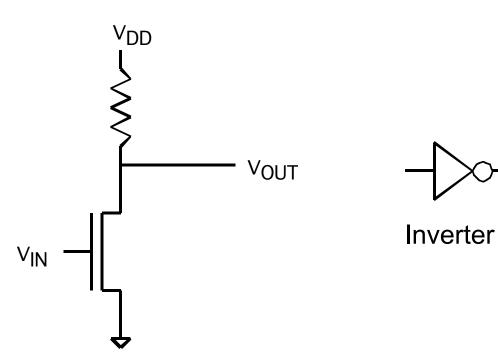

#### Logic gates in nMOS

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

#### Problems with nMOS

- Static current draw

- When the transistor is on, there is a path from  $V_{DD}$  to ground

- More power drain

- Logic high output does not go all the way to VDD

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

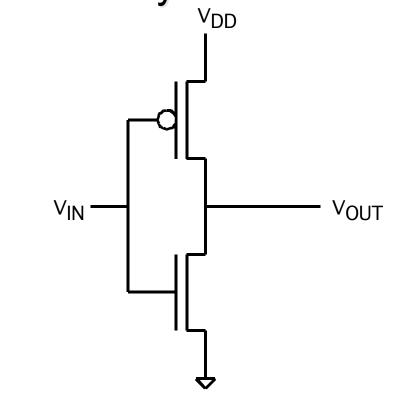

Complementary MOS

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

# CMOS

- No static current flow

- Less current means less power

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1

#### Next class

• Read Chapters 1, 2 and 3 of book

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 1