# VLSI Design and Simulation

Lecture 3

**CMOS Inverters**

# **Topics**

- Inverter VTC

- Noise Margin

- Static Load Inverters

### CMOS Inverter First-Order DC Analysis

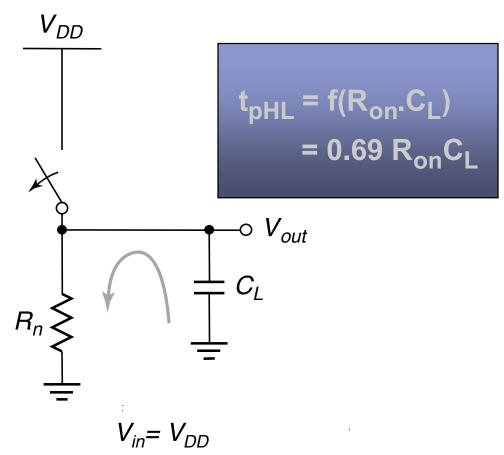

#### **CMOS Inverter: Transient Response**

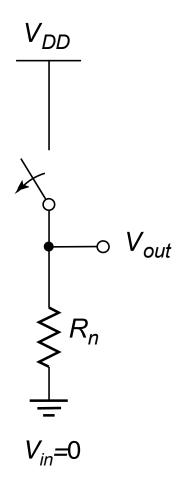

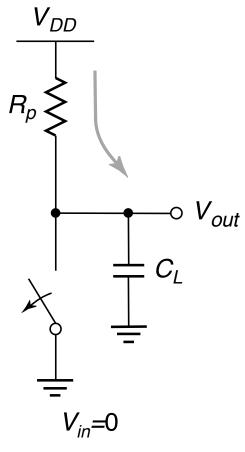

(a) Low-to-high

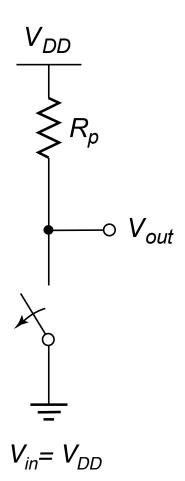

(b) High-to-low

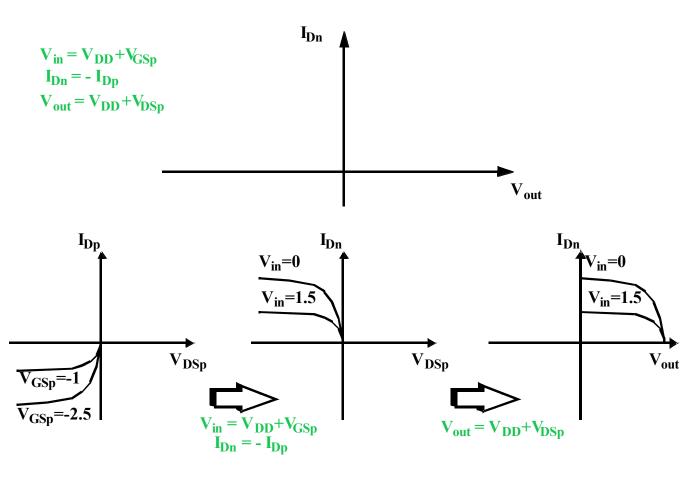

#### **PMOS Load Lines**

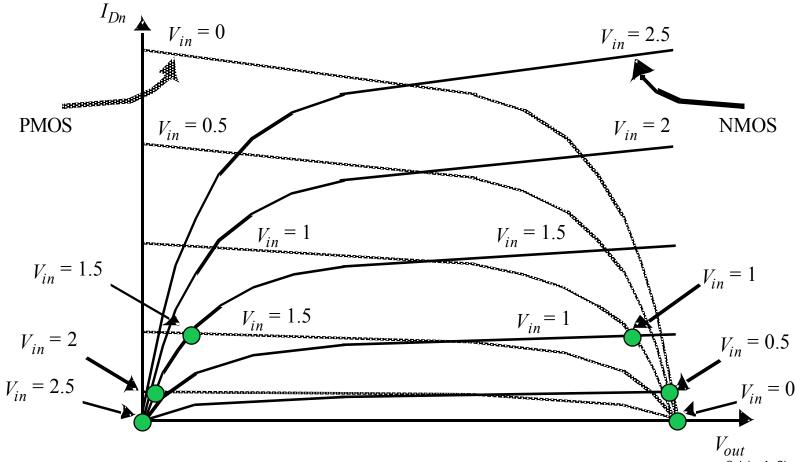

# CMOS Inverter Load Characteristics

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 3 © John A. Chandy Dept. of Electrical and Computer Engineering University of Connecticut

Lecture 3

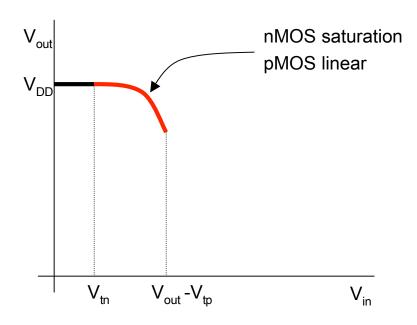

Set pMOS Linear I<sub>DS</sub> equal to nMOS Saturation I<sub>DS</sub>

$$k_{n} \left( \frac{(V_{in} - V_{tn})^{2}}{2} \right) = k_{p} \left( (V_{in} - V_{DD} - V_{tp}) (V_{out} - V_{DD}) - \frac{(V_{out} - V_{DD})^{2}}{2} \right)$$

$$\frac{(V_{out} - V_{DD})^{2}}{2} - (V_{in} - V_{DD} - V_{tp}) (V_{out} - V_{DD}) + \frac{k_{n}}{k_{p}} \frac{(V_{in} - V_{tn})^{2}}{2} = 0$$

$$(V_{out} - V_{DD}) = (V_{in} - V_{DD} - V_{tp}) + \sqrt{(V_{in} - V_{DD} - V_{tp})^{2} - \frac{k_{n}}{k_{p}} (V_{in} - V_{tn})^{2}}$$

$$V_{out} = (V_{in} - V_{tp}) + \sqrt{(V_{in} - V_{DD} - V_{tp})^{2} - \frac{k_{n}}{k_{p}} (V_{in} - V_{tn})^{2}}$$

#### Short channel model

$$k_{n}V_{DSATn}\left(V_{in} - V_{tn} - \frac{V_{DSATn}}{2}\right) = k_{p}\left(\left(V_{in} - V_{DD} - V_{tp}\right)\left(V_{out} - V_{DD}\right) - \frac{\left(V_{out} - V_{DD}\right)^{2}}{2}\right)$$

$$\frac{\left(V_{out} - V_{DD}\right)^{2}}{2} - \left(V_{in} - V_{DD} - V_{tp}\right)\left(V_{out} - V_{DD}\right) + \frac{k_{n}}{k_{p}}V_{DSATn}\left(V_{in} - V_{tn} - \frac{V_{DSATn}}{2}\right) = 0$$

$$\left(V_{out} - V_{DD}\right) = \left(V_{in} - V_{DD} - V_{tp}\right) + \sqrt{\left(V_{in} - V_{DD} - V_{tp}\right)^{2} - 2\frac{k_{n}}{k_{p}}V_{DSATn}\left(V_{in} - V_{tn} - \frac{V_{DSATn}}{2}\right)}$$

$$V_{out} = \left(V_{in} - V_{tp}\right) + \sqrt{\left(V_{in} - V_{DD} - V_{tp}\right)^{2} - 2\frac{k_{n}}{k_{p}}V_{DSATn}\left(V_{in} - V_{tn} - \frac{V_{DSATn}}{2}\right)}$$

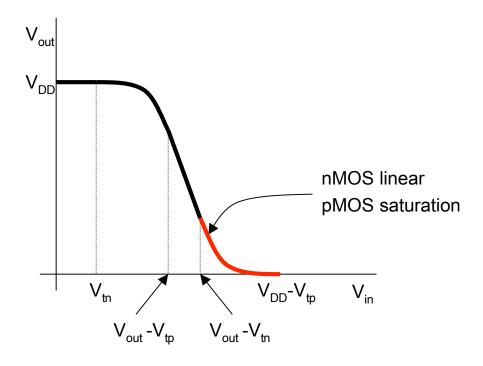

Set nMOS Linear I<sub>DS</sub> equal to pMOS Saturation I<sub>DS</sub>

$$k_{p} \left( \frac{\left( V_{in} - V_{DD} - V_{tp} \right)^{2}}{2} \right) = k_{n} \left( \left( V_{in} - V_{tn} \right) V_{out} - \frac{V_{out}^{2}}{2} \right)$$

$$\frac{V_{out}^{2}}{2} - \left( V_{in} - V_{tn} \right) V_{out} + \frac{k_{p}}{k_{n}} \frac{\left( V_{in} - V_{DD} - V_{tp} \right)^{2}}{2} = 0$$

$$V_{out} = \left( V_{in} - V_{tn} \right) - \sqrt{\left( V_{in} - V_{tn} \right)^{2} - \frac{k_{p}}{k_{n}} \left( V_{in} - V_{DD} - V_{tp} \right)^{2}}$$

#### Short channel model

$$k_{p}V_{DSATp}\left(V_{in} - V_{DD} - V_{tp} - \frac{V_{DSATp}}{2}\right) = k_{n}\left((V_{in} - V_{tn})V_{out} - \frac{V_{out}^{2}}{2}\right)$$

$$\frac{V_{out}^{2}}{2} - (V_{in} - V_{tp})V_{out} + \frac{k_{p}}{k_{n}}V_{DSATp}\left(V_{in} - V_{DD} - V_{tp} - \frac{V_{DSATp}}{2}\right) = 0$$

$$V_{out} = (V_{in} - V_{tn}) - \sqrt{(V_{in} - V_{tn})^{2} - 2\frac{k_{p}}{k_{n}}V_{DSATp}\left(V_{in} - V_{DD} - V_{tp} - \frac{V_{DSATp}}{2}\right)}$$

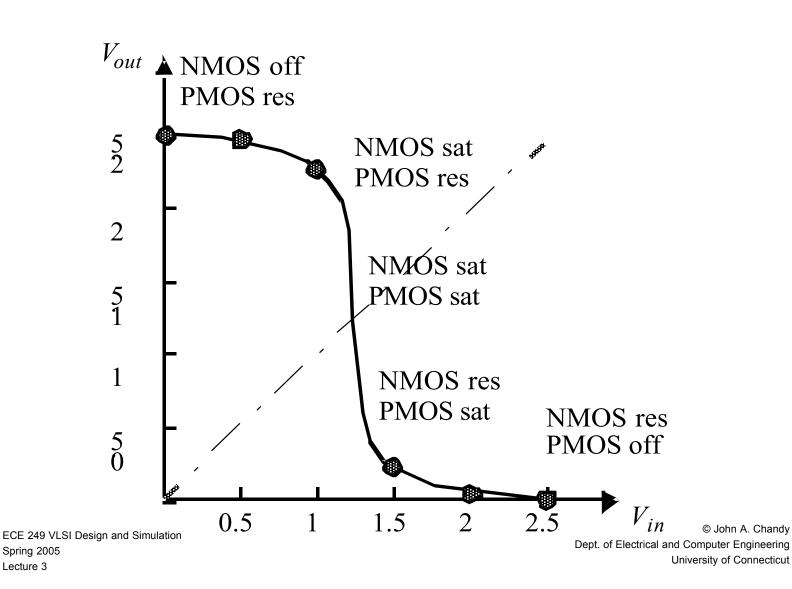

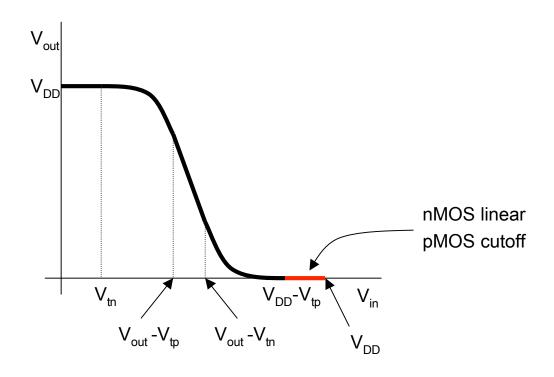

### **CMOS** Inverter

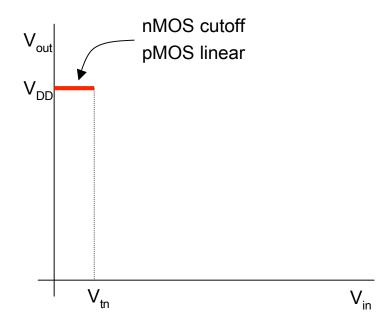

| V <sub>in</sub>                                                                                    | pMOS<br>mode | nMOS<br>mode | $V_{out}$                                                                        |

|----------------------------------------------------------------------------------------------------|--------------|--------------|----------------------------------------------------------------------------------|

| $V_{\underline{in}} < V_{\underline{t}}$                                                           | Linear       | Cutoff       | $V_{\scriptscriptstyle DD}$                                                      |

| $V_{\underline{t}} < V_{\underline{in}} < V_{\underline{out}} V_{\underline{t}}$                   | Linear       | Saturation   | $(V_{in} + V_{t}) + \sqrt{(V_{in} - V_{DD} + V_{t})^{2} - (V_{in} - V_{t})^{2}}$ |

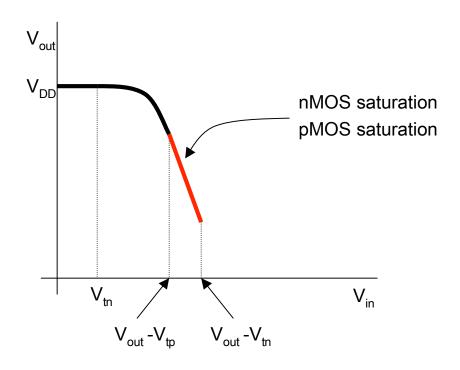

| $V_{\underline{out}}-V_{\underline{t}}< V_{\underline{in}}< V_{\underline{out}}+V_{\underline{t}}$ | Saturation   | Saturation   | Interpolate                                                                      |

| $V_{\underline{out}}+V_{\underline{t}}< V_{\underline{in}}< V_{\underline{DD}}-V_{\underline{t}}$  | Saturation   | Linear       | $(V_{in} - V_t) - \sqrt{(V_{in} - V_t)^2 - (V_{in} - V_{DD} + V_t)^2}$           |

| $V_{\underline{in}} > V_{\underline{DD}} - V_{\underline{t}}$                                      | Cutoff       | Linear       | 0                                                                                |

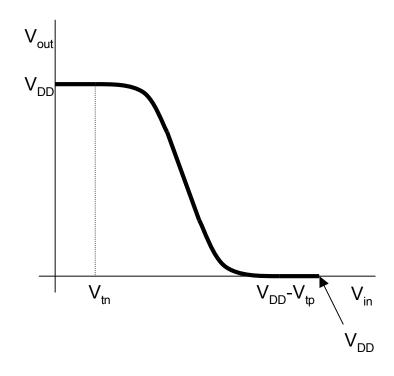

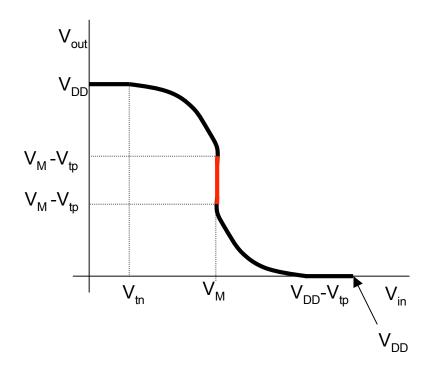

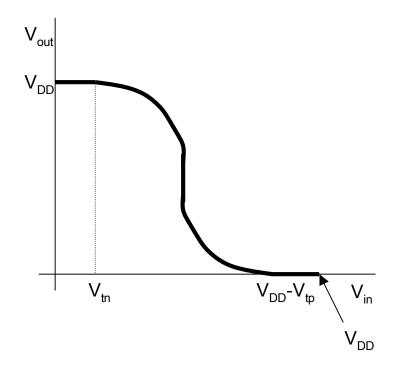

## Switching Threshold

The point at which the inverter has both transistors in saturation

$$\frac{k_n}{2} (V_M - V_{tn})^2 = -\frac{k_p}{2} (V_M - V_{DD} - V_{tp})^2$$

$$(V_M - V_{tn}) = -\sqrt{\frac{-k_p}{k_n}} (V_M - V_{DD} - V_{tp})$$

$$V_M (1+r) = V_{tn} + r(V_{DD} + V_{tp})$$

$$V_M = \frac{V_{tn} + r(V_{DD} + V_{tp})}{1+r}$$

# Switching Threshold

$$V_M = \frac{r(V_{DD} + V_{tp}) + V_{tn}}{1 + r}$$

When V<sub>tn</sub>=-V<sub>tp</sub> and r=1,

$$V_M = \frac{V_{DD}}{2}$$

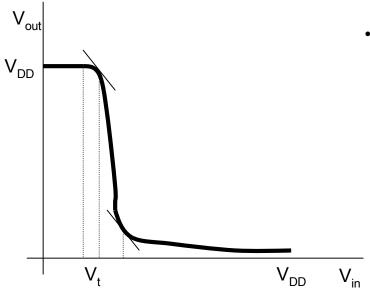

In switching region, the curve is actually vertical; V<sub>out</sub> can have multiple values

# Switching Threshold

With short-channel devices

$$\begin{split} k_{n}V_{DSATn}\bigg(V_{M}-V_{tn}-\frac{V_{DSATn}}{2}\bigg) &= -k_{p}V_{DSATp}\bigg(V_{M}-V_{DD}-V_{tp}-\frac{V_{DSATp}}{2}\bigg) \\ \bigg(V_{M}-V_{tn}-\frac{V_{DSATn}}{2}\bigg) &= -\frac{k_{p}V_{DSATp}}{k_{n}V_{DSATn}}\bigg(V_{M}-V_{DD}-V_{tp}-\frac{V_{DSATp}}{2}\bigg) \\ V_{M}\bigg(1+\frac{k_{p}V_{DSATp}}{k_{n}V_{DSATn}}\bigg) &= V_{tn}+\frac{V_{DSATn}}{2}-\frac{k_{p}V_{DSATp}}{k_{n}V_{DSATn}}\bigg(-V_{DD}-V_{tp}-\frac{V_{DSATp}}{2}\bigg) \\ V_{M} &= \frac{V_{tn}+\frac{V_{DSATn}}{2}+r\bigg(V_{DD}+V_{tp}+\frac{V_{DSATp}}{2}\bigg)}{1+r} \end{split}$$

$$V_M = V_{DD} \frac{r}{1+r}$$

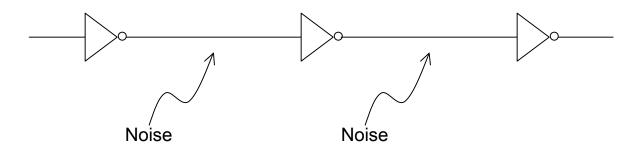

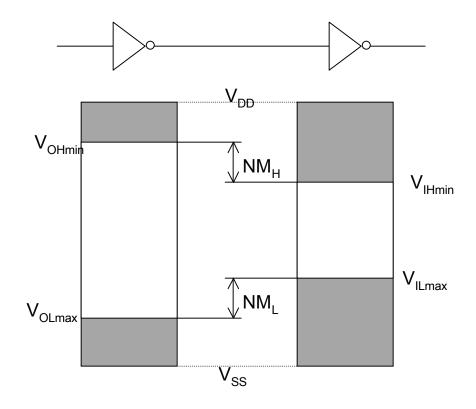

A measure of the acceptable noise at a gate input so that the output is not affected.

# Noise Budget

- Allocates gross noise margin to expected sources of noise

- Sources: supply noise, cross talk, interference, offset

- Differentiate between fixed and proportional noise sources

# Key Reliability Properties

- Absolute noise margin values are deceptive

- a floating node is more easily disturbed than a node driven by a low impedance (in terms of voltage)

- Noise immunity is the more important metric the capability to suppress noise sources

- Key metrics: Noise transfer functions, Output impedance of the driver and input impedance of the receiver;

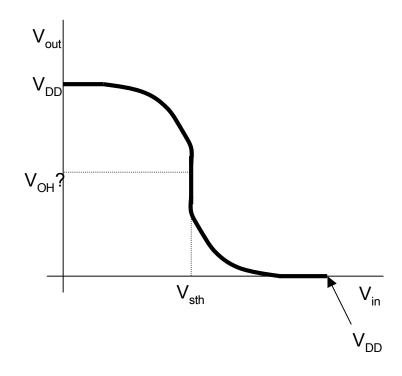

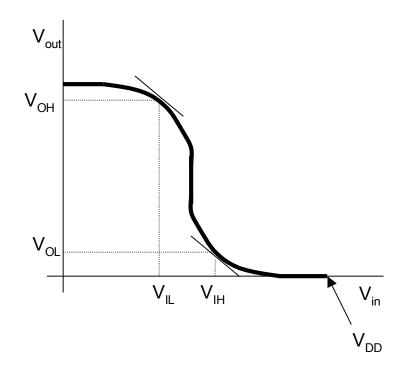

- Obvious choice

- Set V<sub>IH</sub>=V<sub>IL</sub>=V<sub>M</sub>

- No noise margin

- High gain at  $V_{IH}$  and  $V_{IL}$

- Any perturbations could cause incorrect values

- Set  $V_{IL} = V_{tn}$  and  $V_{IH} = V_{DD} V_{tp}$

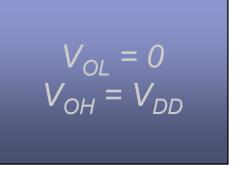

- $\cdot V_{OL} = 0$  and  $V_{OH} = V_{DD}$

- Too restrictive

Voltage Transfer Function

$$V_{out} = f(V_{in})$$

Voltage Transfer Function with Noise

$$\begin{split} V_{out} &= f \big( V_{in} + \Delta V_{noise} \big) \\ V_{out} &\approx f \big( V_{in} \big) + \frac{d V_{out}}{d V_{in}} \Delta V_{noise} \end{split}$$

- Perturbed voltage is the sum of the nominal output plus the gain times the noise

- Keep the gain less than 1

Setting the derivative to -1 and solving

$$V_{IH} = V_{M} + V_{M} \frac{(V_{M} - V_{Tn} - V_{DSATn}/2)(\lambda_{n} - \lambda_{p})}{1 + r}$$

$$V_{IL} = V_{M} - (V_{DD} - V_{M}) \frac{(V_{M} - V_{Tn} - V_{DSATn}/2)(\lambda_{n} - \lambda_{p})}{1 + r}$$

• Assuming

$$r = 1, V_{Tn} = -V_{Tp}, V_{DSATn} = -V_{DSATp}$$

$$V_{IH} = \frac{V_{DD}}{2} \left[ 1 + \left( \frac{V_{DD}}{2} - V_T - \frac{V_{DSAT}}{2} \right) \frac{\left( \lambda_n - \lambda_p \right)}{2} \right]$$

$$V_{IL} = \frac{V_{DD}}{2} \left[ 1 - \left( \frac{V_{DD}}{2} - V_T - \frac{V_{DSAT}}{2} \right) \frac{\left( \lambda_n - \lambda_p \right)}{2} \right]$$

ECE 249 VLSI Design and Simulation 2

Dept. of Electrical and Computer Engineering University of Connecticut

•

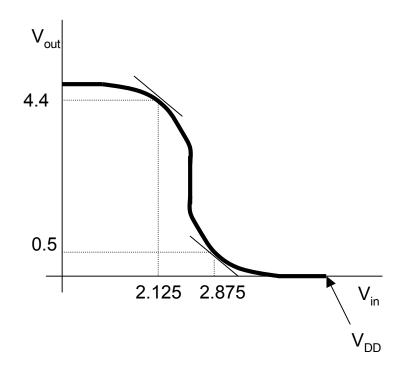

$$V_t = 0.5 V$$

•

$$\lambda = 0.1$$

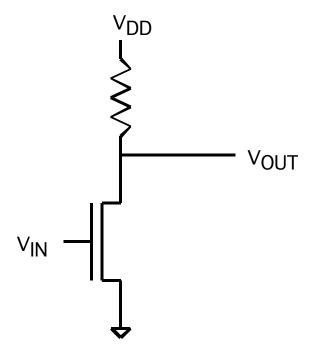

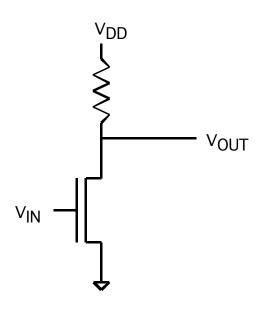

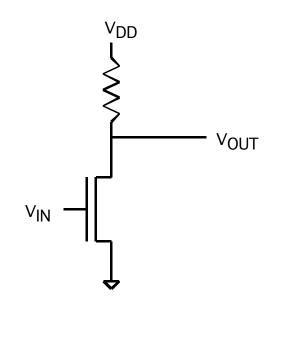

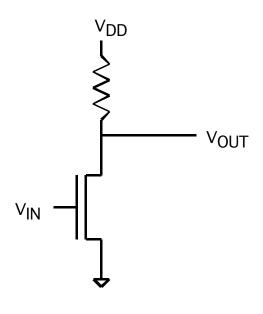

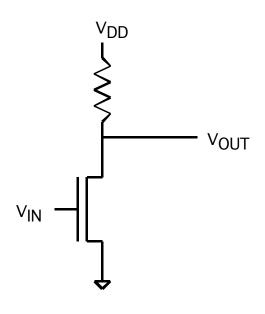

Transistor is in saturation

$$I_{DS} = k_n \frac{(V_{GS} - V_T)^2}{2} (1 + \lambda V_{DS})$$

$$V_{OUT} = V_{DD} - Rk_n \frac{(V_{IN} - V_T)^2}{2} (1 + \lambda V_{OUT})$$

$$V_{OUT} = \frac{2V_{DD} - Rk_n (V_{IN} - V_T)^2}{2 + \lambda Rk_n (V_{IN} - V_T)^2}$$

#### Transistor is in linear region

$$I_{DS} = k_n \left[ (V_{GS} - V_T) V_{DS} - \frac{{V_{DS}}^2}{2} \right]$$

$$V_{OUT} = V_{DD} - Rk_n \left[ (V_{IN} - V_T) V_{OUT} - \frac{V_{OUT}^2}{2} \right]$$

$$\frac{Rk_n}{2}V_{OUT}^2 - (Rk_n(V_{IN} - V_T) + 1)V_{OUT} + V_{DD} = 0$$

$$V_{OUT} = (V_{IN} - V_T) + \frac{1}{Rk_n} - \sqrt{(V_{IN} - V_T) + \frac{1}{Rk_n}^2 - 2\frac{V_{DD}}{Rk_n}}$$

$$V_{IL} = V_T + \frac{1}{k_n R}$$

$$V_{IH} = V_T + \sqrt{\frac{8}{3} \frac{V_{DD}}{k_n R}} - \frac{1}{k_n R}$$

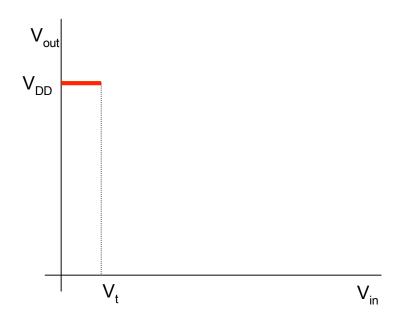

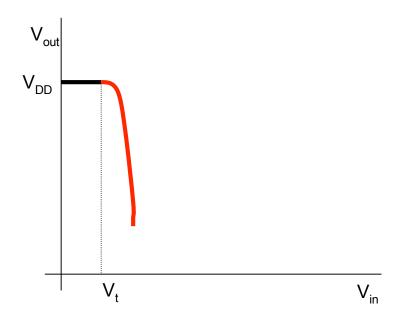

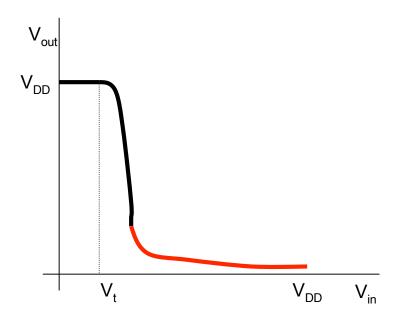

- Does not go down all the way to 0

- Noise margins are tighter

- Switching threshold is not centered

- To get high gain in the transition region, you need bigger resistors

#### Homework

- Due February 3rd

- Read Chapter 2