# VLSI Design and Simulation

Lecture 4

**CMOS Processing Technology**

#### Topics

CMOS Processing Technology

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

- How do we make a transistor?

- Fabrication Process

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

- Silicon single crystal growth from polysilicon

- Silicon ingot with impurities is created

- Ingot diameter can vary from 100mm to 300mm

- Wafers are sliced from the ingot

- Typically 300-600µm thick

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

- Why the trend to larger wafers?

- More chips per wafer

- Less waste

- After slicing

- Lapping

- Polishing

- Defect detection

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

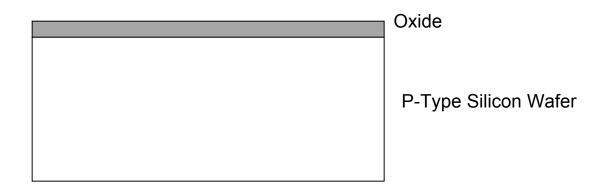

- Oxide Layer SiO<sub>2</sub> (sand)

- Heat Wafer in an oxidizing atmosphere water vapor or pure oxygen gas

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

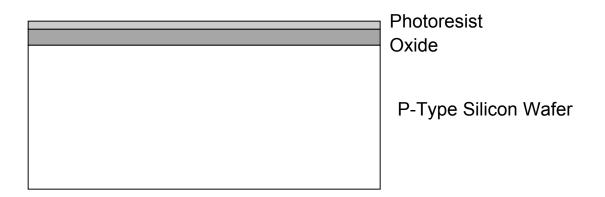

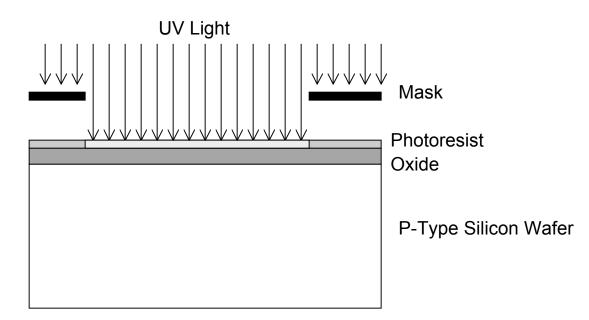

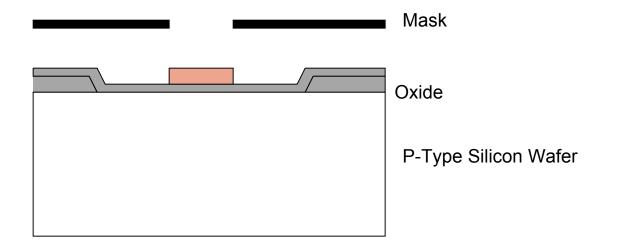

- How do you control where the features get placed?

- Photolithography masks

| Oxide                |

|----------------------|

| P-Type Silicon Wafer |

|                      |

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

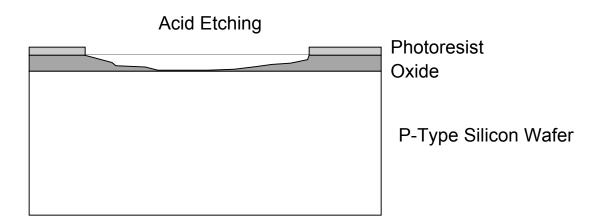

• Need to remove the oxide layer

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

• Need to remove the oxide layer

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

• Need to remove the oxide layer

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

• Add polysilicon layer for gate

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

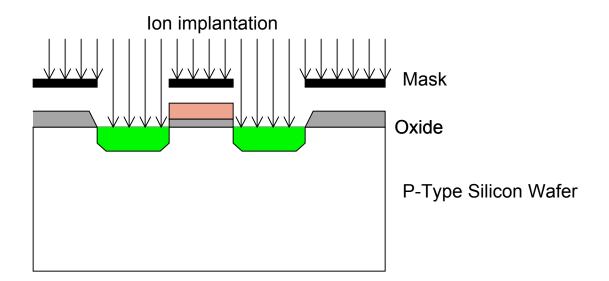

- Impurity injection

- Diffusion

- Wafers are placed in a heated tube with dopant gas

- At high temperatures (~1000°C), the dopant diffuses into the exposed regions of the wafer

- Ion Implantation

- Dopants are introduced as ions into material by sweeping a beam across the material

- Depth of implantation and density is controlled by the acceleration and exposure time

- High energy implantation can cause lattice damage

- Deposition

- Deposit a gas or vapor (CVD) on the wafer at high temperatures

Impurity injection

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

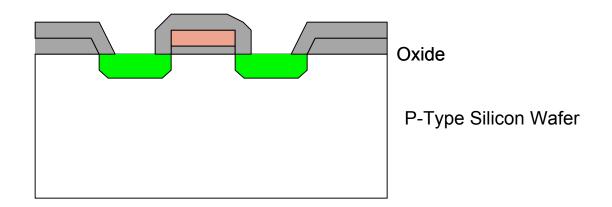

Add Oxide insulation layer

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

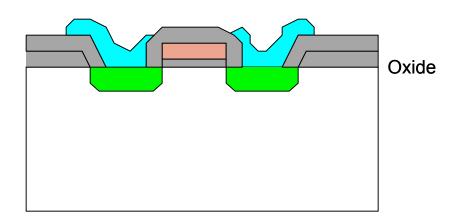

Add Metal layer

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

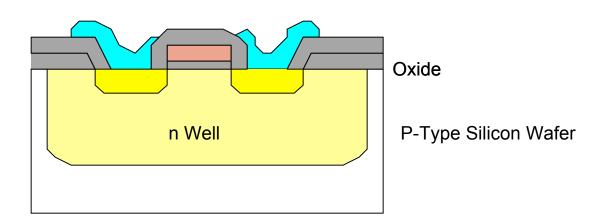

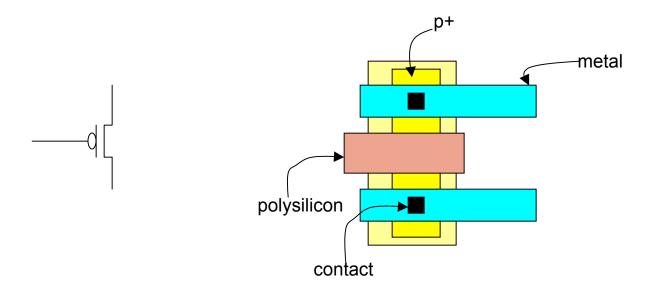

pMOS Transistor

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

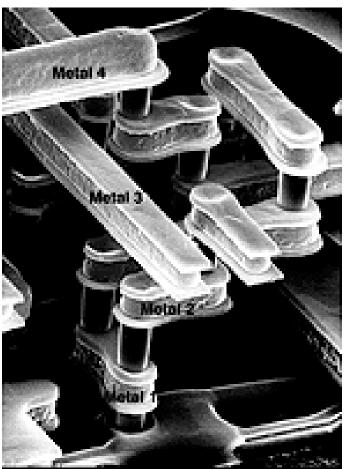

#### Interconnect

- Polysilicon to Metal contacts

- Diffusion to Metal contacts

- Diffusion to Polysilicon silicide contacts

- Metal to Metal vias

#### Metallization

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

# Packaging Requirements

- Electrical: Low parasitics

- Mechanical: Reliable and robust

- Thermal: Efficient heat removal

- Economical: Cheap

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

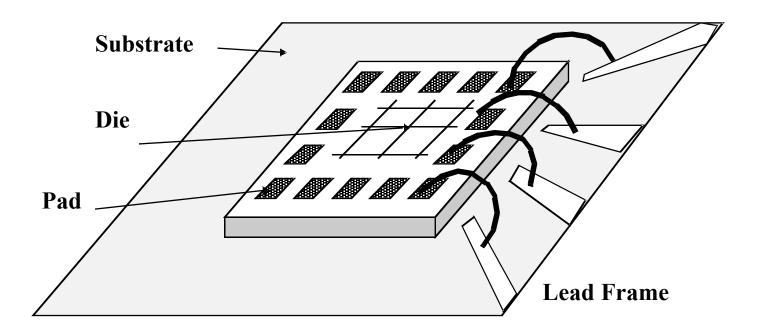

# **Bonding Techniques**

#### **Wire Bonding**

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

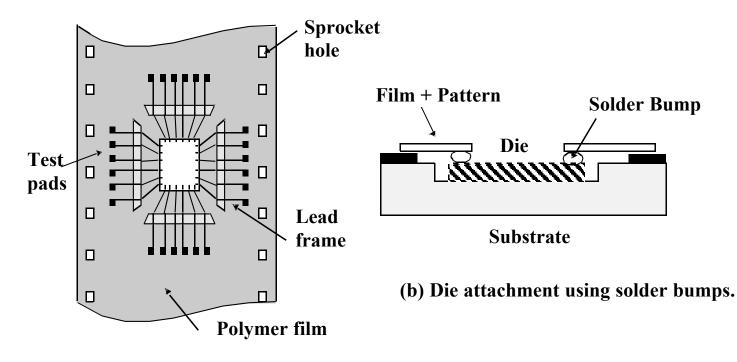

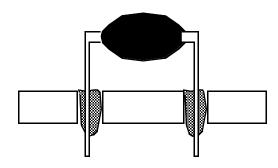

# Tape-Automated Bonding (TAB)

(a) Polymer Tape with imprinted wiring pattern.

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

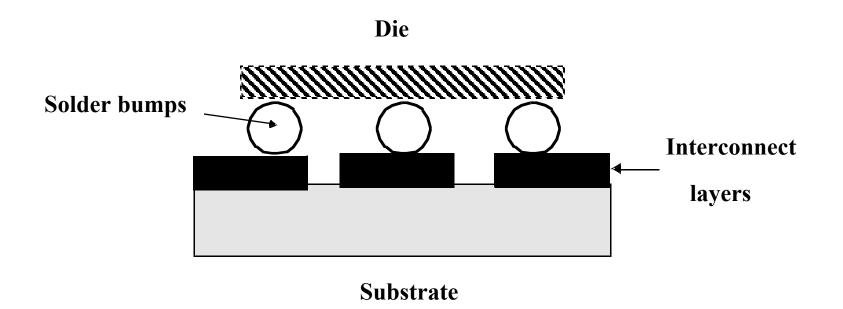

# Flip-Chip Bonding

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

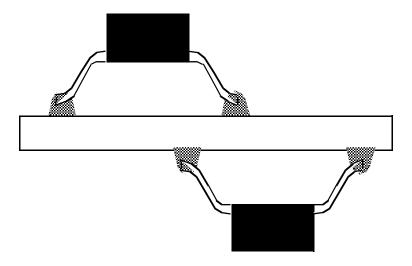

#### Package-to-Board Interconnect

(a) Through-Hole Mounting

(b) Surface Mount

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

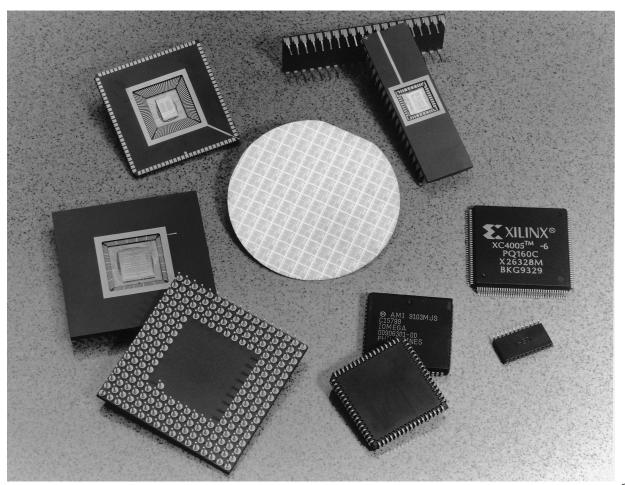

### Package Types

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

# Package Parameters

| Package Type           | Capacitance<br>(pF) | Inductance<br>(nH) |

|------------------------|---------------------|--------------------|

| 68 Pin Plastic DIP     | 4                   | 35                 |

| 68 Pin Ceramic DIP     | 7                   | 20                 |

| 256 Pin Pin Grid Array | 5                   | 15                 |

| Wire Bond              | 1                   | 1                  |

| Solder Bump            | 0.5                 | 0.1                |

Typical Capacitances and Inductances of Various Package and Bonding Styles (from [Sze83])

# Trends in Process Technology

- Copper Conductors

- Silicon on Insulator

- Strained Silicon

- Three-dimensional ICs

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

# **Multi-Chip Modules**

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

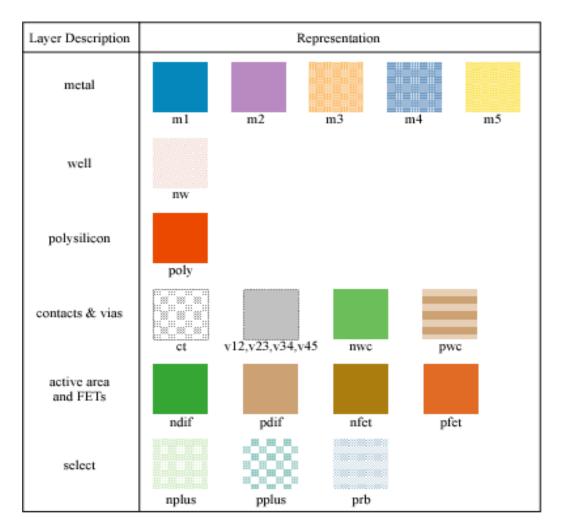

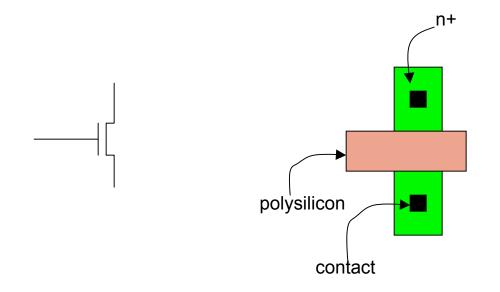

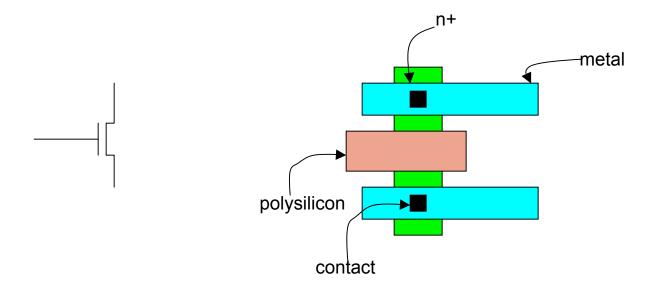

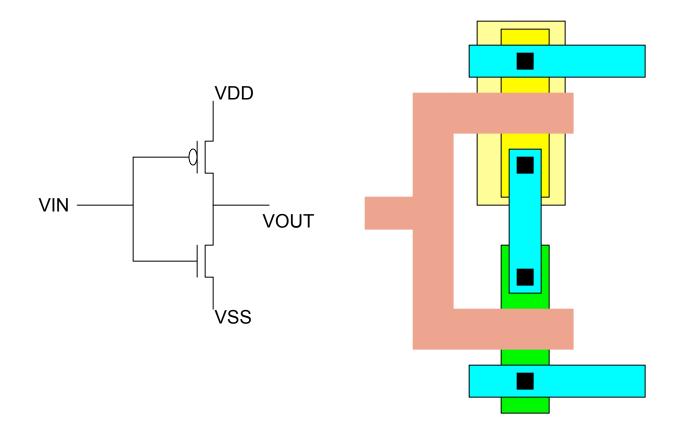

# **CMOS Process Layers**

| Layer                | Color   | Representation |

|----------------------|---------|----------------|

| Well (p,n)           | Yellow  |                |

| Active Area (n+,p+)  | Green   |                |

| Select (p+,n+)       | Green   | C              |

| Polysilicon          | Red     |                |

| Metal1               | Blue    |                |

| Metal2               | Magenta |                |

| Contact To Poly      | Black   |                |

| Contact To Diffusion | Black   |                |

| Via                  | Black   |                |

|                      |         |                |

# Layers in 0.25 µm CMOS process

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

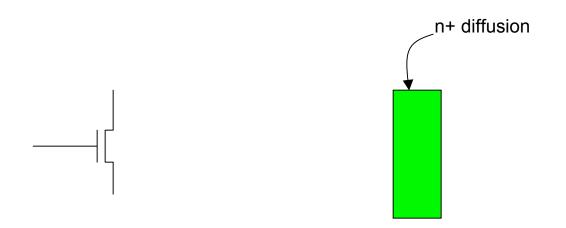

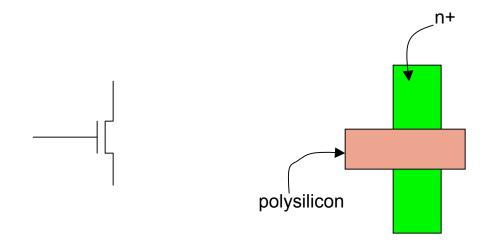

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

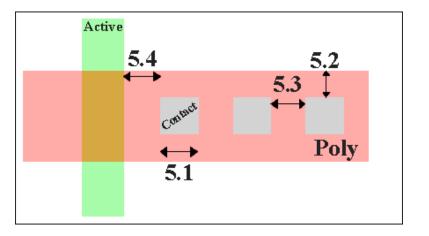

# **Design rules**

- Design rules are critical to proper operation of the circuit

- They place restrictions on the sizes of layers and the distance between layers

- Often expressed in terms of  $\lambda$  half the minimum feature size

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

# **Design Rules**

| MOSIS SCMOS Design Rules |                                       |     |  |

|--------------------------|---------------------------------------|-----|--|

| 5.1                      | Contact size                          | 2x2 |  |

| 5.2                      | Minimum poly overlap                  | 1.5 |  |

| 5.3                      | Minimum contact spacing               | 2   |  |

| 5.4                      | Minimum spacing to gate of transistor | 2   |  |

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

NMOS

© John A. Chandy Dept. of Electrical and Computer Engineering University of Connecticut

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

NMOS

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

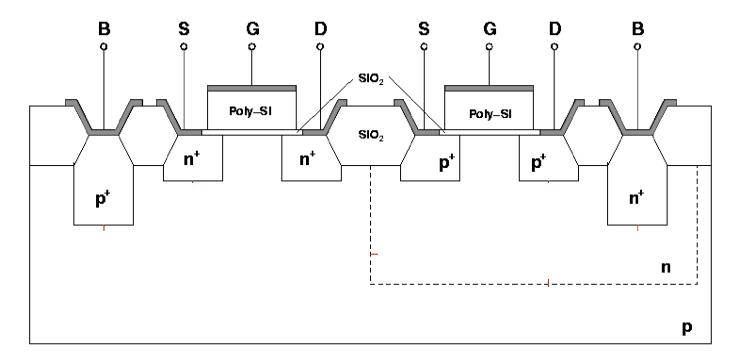

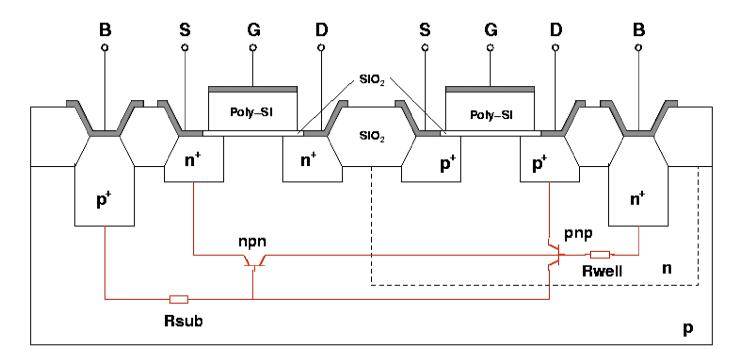

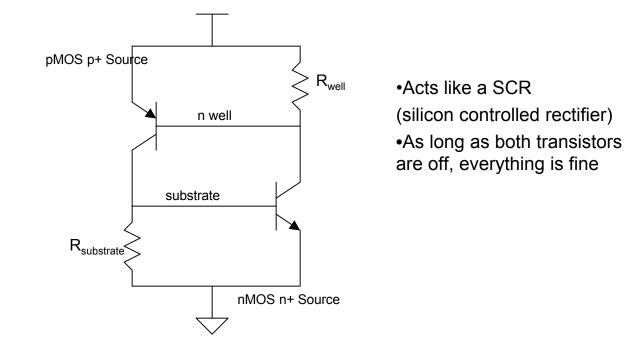

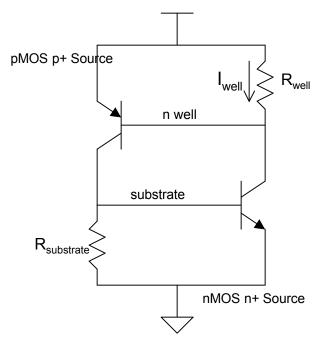

•External disturbance causes current flow in  $\rm R_{sub}$  or  $\rm R_{well}$

•Feedback loop will cause the current draw to increase dramatically

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4

- External disturbances

- ESD (electrostatic discharge) stress

- Cosmic rays/alpha particles

- Sudden transients on Vdd or Gnd

- I/O pads interfacing with large currents off chip

- Avoiding latchup

- Decrease  $R_{\text{sub}}$  and  $R_{\text{well}}$  so that it is harder to turn on the BJT transistors

- Place substrate and well contacts close together

- Keep pMOS transistors close to Vdd and nMOS transistors close to ground

- Surround transistors in I/O pads with guard rings

- Decrease  $\beta$  of BJT transistors

- Space the pMOS and nMOS transistors apart

#### Next Class

- Performance Characterization

- Read Chapter 4

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 4