#### Topics

- CMOS Design

- Multi-input delay analysis

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

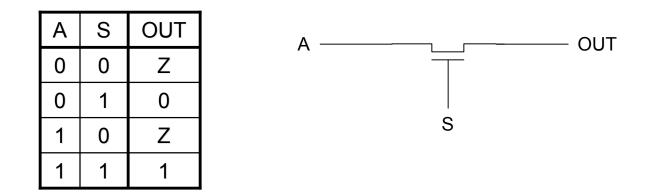

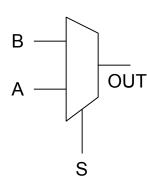

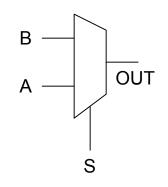

Transmission Gate

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

Transmission Gate

- When S is low, the output is at high impedance

- When S is high, the output follows A

- However, OUT can only rise to  $V_{DD}$ - $V_{T_{1}}$  at which point the transistor will shut off

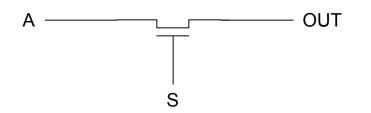

Transmission Gate

- When S is high, the output is at high impedance

- When S is low, the output follows A

- However, OUT can only fall to  $V_{T_{\tau}}$  at which point the transistor will shut off

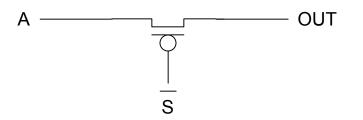

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

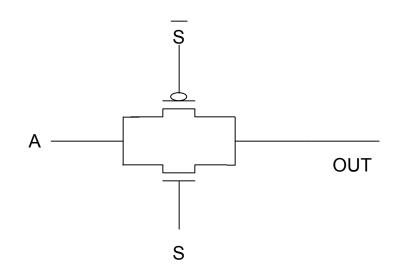

- Transmission gate

- Requires both nMOS and pMOS transistors

- Single nMOS or single pMOS will cause signal degradation

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

Transmission Gate

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

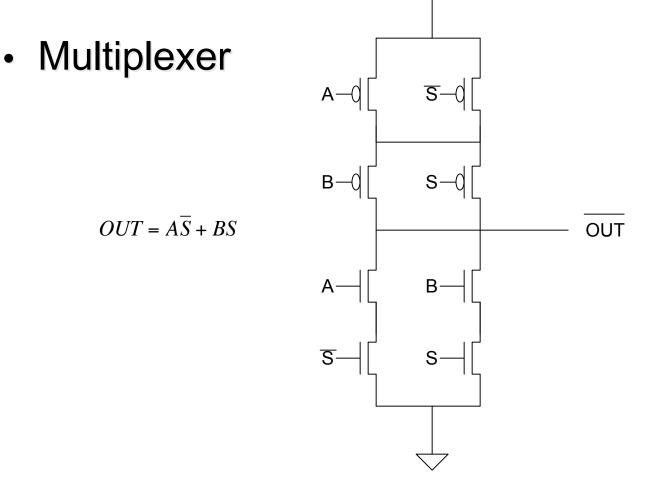

#### Multiplexer

| А | В | S | OUT |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 1   |

$OUT = A\overline{S} + BS$

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

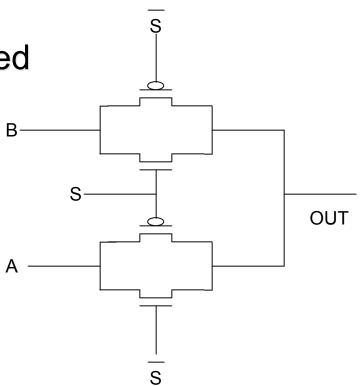

• Multiplexer

- Transmission gate based

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

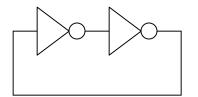

Memory

- Use feedback loops to store bits

– How do you get the bit in the loop?

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

- Memory

- Use transmission gates to control entry to the loop

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

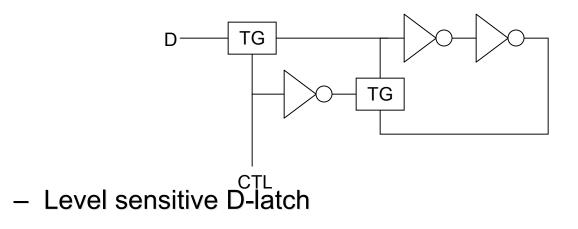

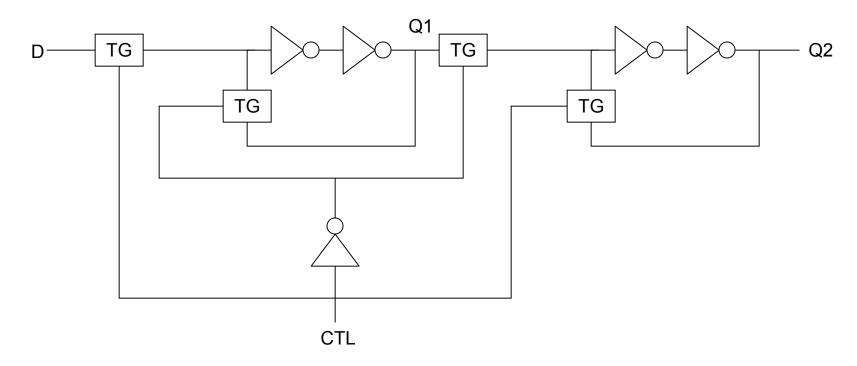

- Latches

- Level sensitive latches do not allow you to isolate output from input when control is high.

- Solution is to use a master-slave setup where master latches input and then slave latches the output

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

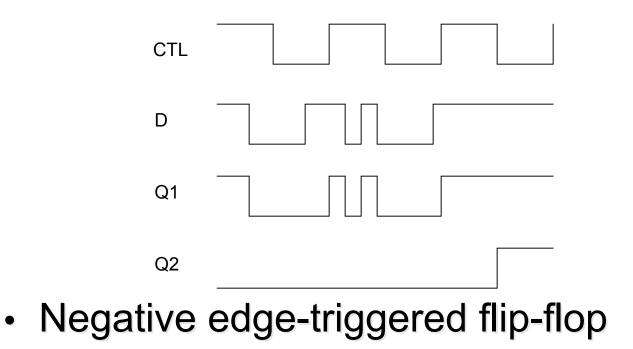

Master -slave latch

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

Master -slave latch

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

# CMOS Logic

- Setup time is how much time <u>before</u> the clock edge that the data should be ready

- If setup time is not met, the data will not have time to get through transmission gate and into the feedback loop

- Hold time is the time that the data is required to be stable <u>after</u> the clock edge.

- If hold time is not met, invalid data may get past the transmission gate and into the feedback loop.

## **CMOS Logic**

#### Flip-Flops

| D | Q0 | Q1 |

|---|----|----|

| 0 | Х  | 0  |

| 1 | Х  | 1  |

| S | R | Q0 | Q1 |

|---|---|----|----|

| 0 | 0 | 0  | 0  |

| 0 | 0 | 1  | 1  |

| 0 | 1 | Х  | 0  |

| 1 | 0 | Х  | 1  |

| 1 | 1 | Х  | Х  |

| _ |   |    |    |

|---|---|----|----|

| J | Κ | Q0 | Q1 |

| 0 | 0 | 0  | 0  |

| 0 | 0 | 1  | 1  |

| 0 | 1 | Х  | 0  |

| 1 | 0 | Х  | 1  |

| 1 | 1 | 0  | 1  |

| 1 | 1 | 1  | 0  |

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

## **CMOS Logic**

- Registers

- N-bit collection of flip-flops

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

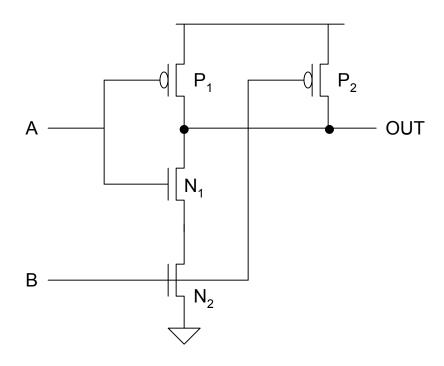

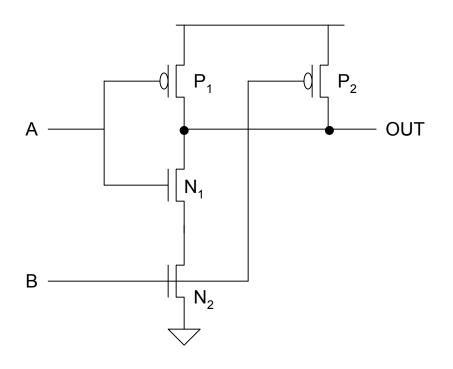

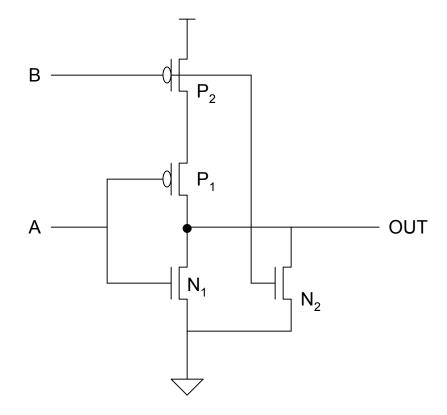

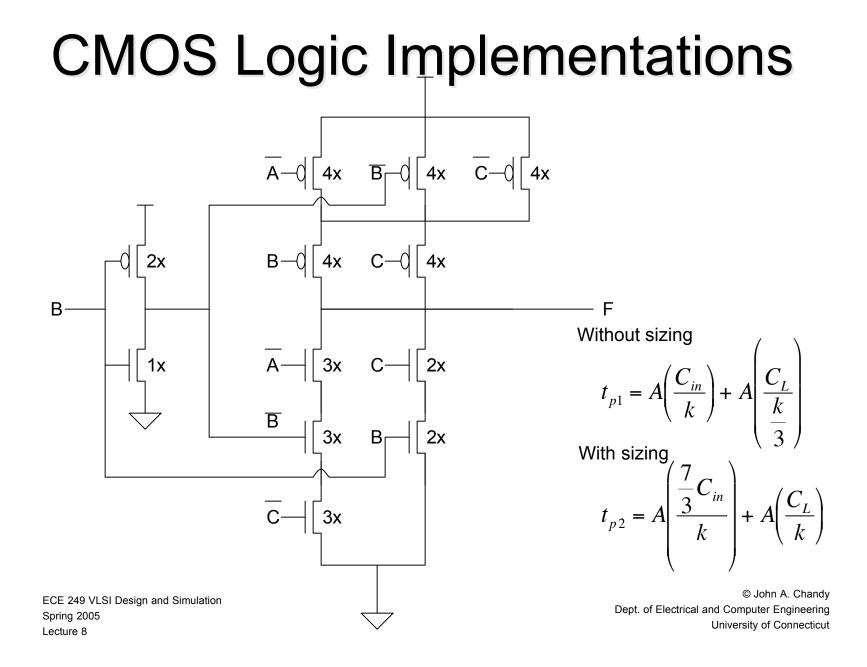

## CMOS Logic Gate Design

How do you characterize delay for a gate more complicated than an inverter?

$$t_d = A \frac{C_L}{k_{eff}}$$

•  $k_{eff}$  is determined by the structure of the logic gate

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

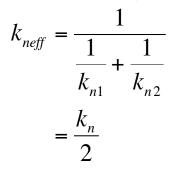

#### Delay time analysis

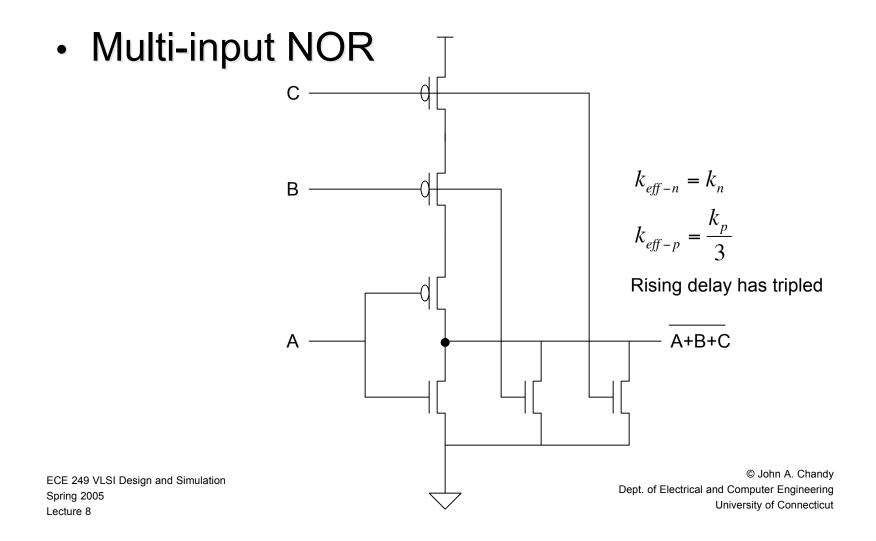

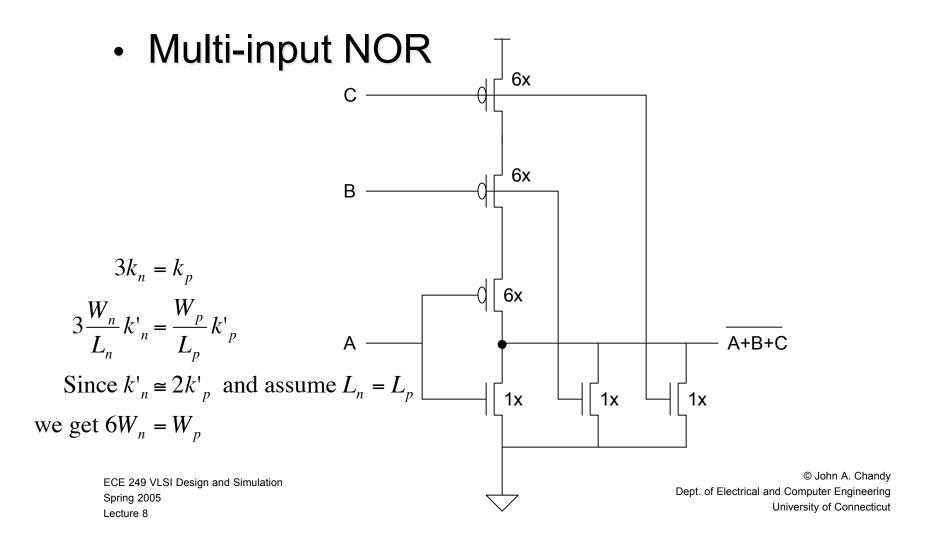

Multi-input gates

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8 •For pull down (falling delay time)

•For pull up (rising delay time)

$$k_{peff} = k_p$$

#### NAND

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

#### Delay time analysis

Multi-input gates

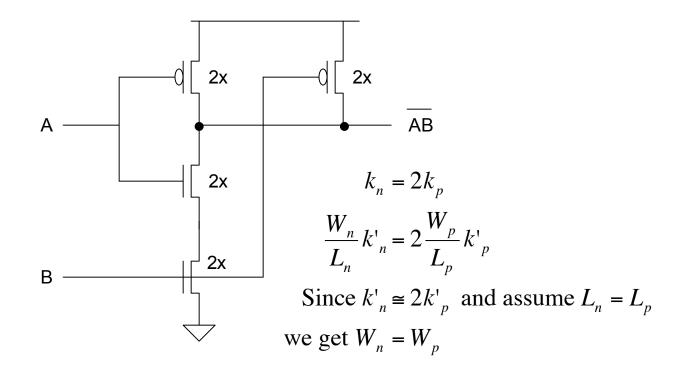

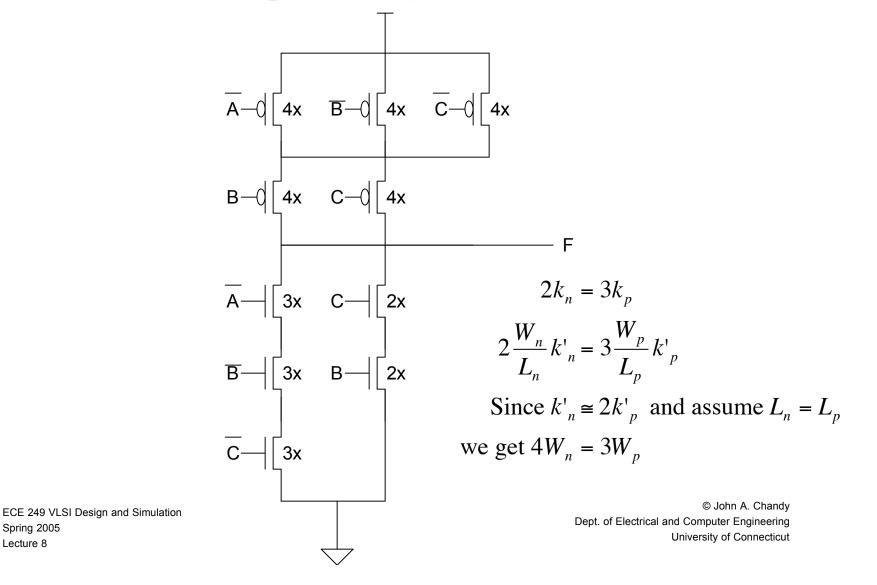

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8 •For equal delay times

$$k_n = 2k_p$$

$$\frac{W_n}{L_n}k'_n = 2\frac{W_p}{L_p}k'_p$$

#### NAND

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

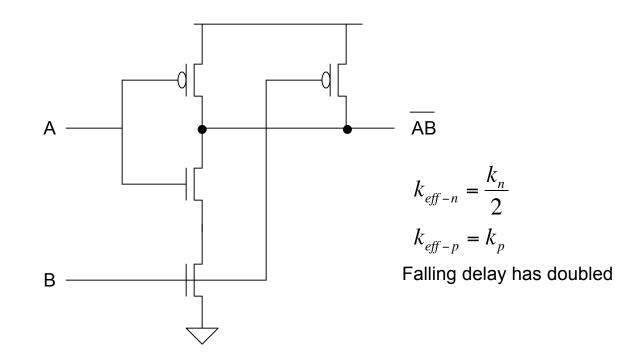

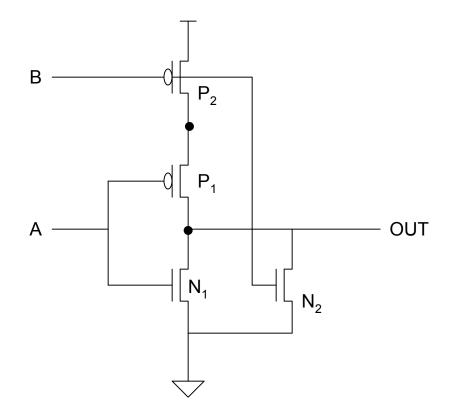

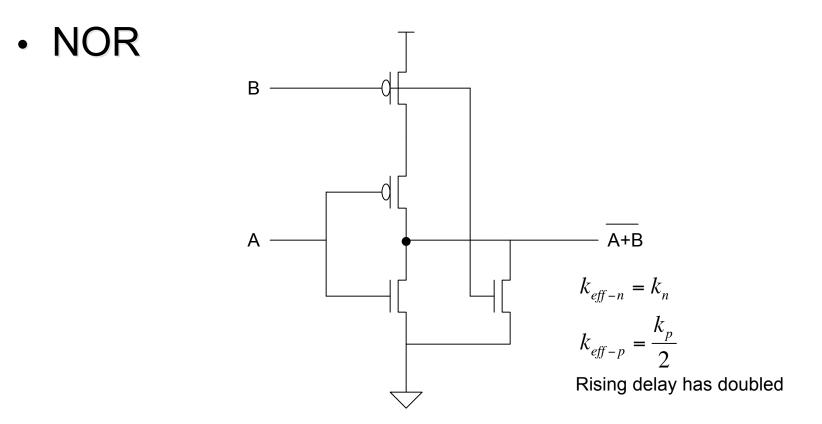

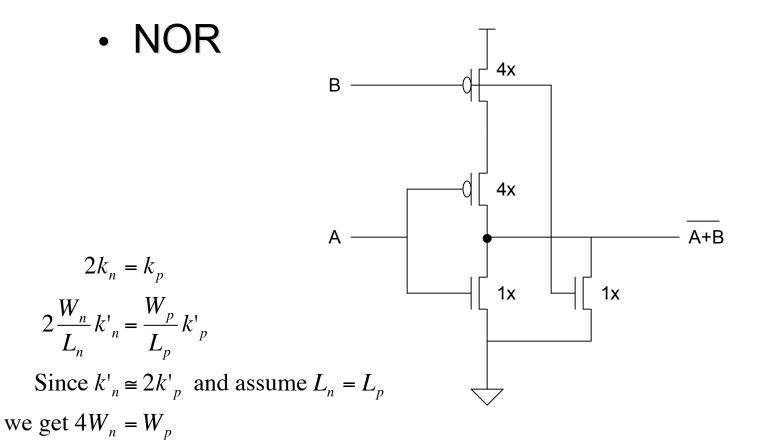

#### Delay time analysis

•For pull down (falling delay time)

$k_{n-eff} = k_n$  (single transistor on)

•For pull up (rising delay time)

$$k_{p-eff} = \frac{1}{\frac{1}{k_{p1}} + \frac{1}{k_{p2}}}$$

$$= \frac{k_p}{2}$$

© John A. Chandy Dept. of Electrical and Computer Engineering University of Connecticut

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

#### Delay time analysis

•For equal delay times

$$2k_n = k_p$$

$$2\frac{W_n}{L_n}k'_n = \frac{W_p}{L_p}k'_p$$

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

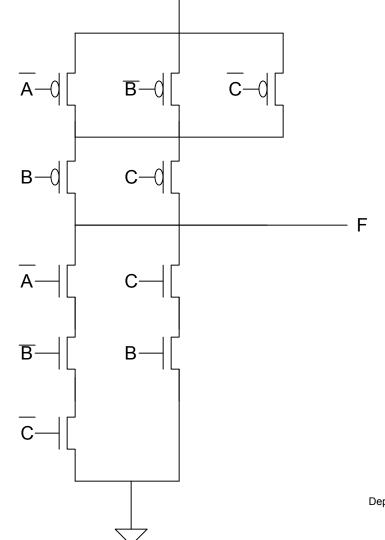

$k_{eff-n} = \frac{k_n}{3}$  $k_{eff-p} = \frac{k_p}{2}$

Falling delay has tripled Rising delay has doubled

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8

Spring 2005

Lecture 8

## CMOS Logic Gate Delays

- Increasing transistor sizes can reduce the delays, but it

- Increases area

- Increases load capacitance for driving gates

- Multi-input gates may not always be good

#### Next class

- Gate Delays

- Logical Effort

- Chapter 6.2

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 8