# Topics

- Dynamic CMOS

- Sequential Design

- Memory and Control

# Dynamic CMOS

In static circuits at every point in time (except when switching) the output is connected to either GND or V<sub>DD</sub> via a low resistance path.

- fan-in of *n* requires 2n (*n* N-type + *n* P-type) devices

- Dynamic circuits rely on the temporary storage of signal values on the capacitance of high impedance nodes.

- requires only n+2 (n+1 N-type + 1 P-type) transistors

# Dynamic CMOS

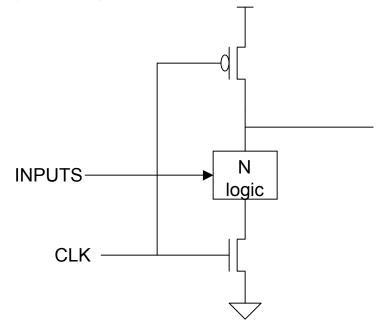

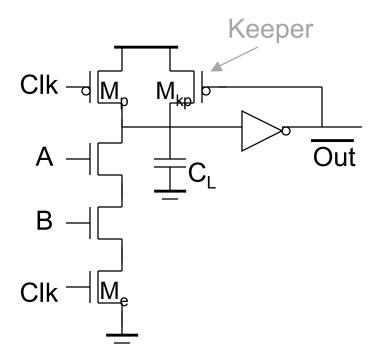

nMOS logic structure with precharged pullup

Precharge to VDD when clock is lowEvaluate when clock is high

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

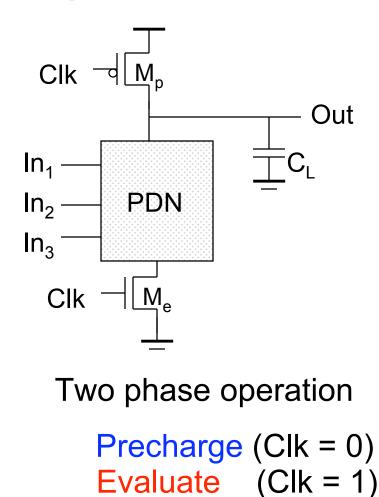

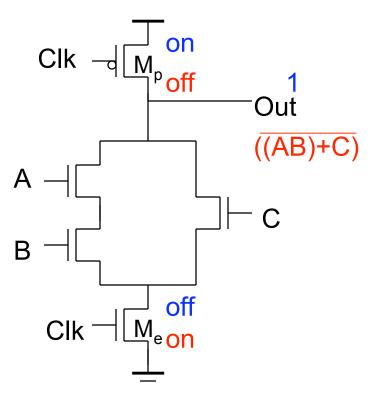

# **Dynamic Gate**

© John A. Chandy Dept. of Electrical and Computer Engineering University of Connecticut

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

# **Conditions on Output**

- Once the output of a dynamic gate is discharged, it cannot be charged again until the next precharge operation.

- Inputs to the gate can make at most one transition during evaluation.

- Output can be in the high impedance state during and after evaluation (PDN off), state is stored on C<sub>L</sub>

# **Properties of Dynamic Gates**

- Logic function is implemented by the PDN only

- number of transistors is N + 2 (versus 2N for static complementary CMOS)

- Full swing outputs ( $V_{OL}$  = GND and  $V_{OH}$  =  $V_{DD}$ )

- Non-ratioed sizing of the devices does not affect the logic levels

- Faster switching speeds

- reduced load capacitance due to lower input capacitance (C<sub>in</sub>)

- reduced load capacitance due to smaller output loading (Cout)

- no  $I_{sc}$ , so all the current provided by PDN goes into discharging  $C_L$

# Properties of Dynamic Gates

- Overall power dissipation usually higher than static CMOS

- no static current path ever exists between  $V_{\text{DD}}$  and GND (including  $P_{\text{sc}})$

- no glitching

- higher transition probabilities

- extra load on Clk

- PDN starts to work as soon as the input signals exceed  $V_{Tn},$  so  $V_M,\,V_{IH}$  and  $V_{IL}$  equal to  $V_{Tn}$

- low noise margin (NM<sub>L</sub>)

- Needs a precharge/evaluate clock

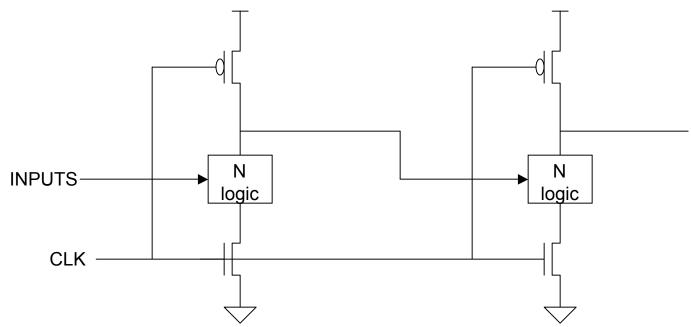

# Dynamic CMOS

- Advantages

- Fewer transistors than CMOS on the same order as pseudo-nMOS

- Smaller load capacitances faster speed

- Disadvantages

- Inputs must be stable during evaluate phase

- Can not be cascaded

- Charge sharing

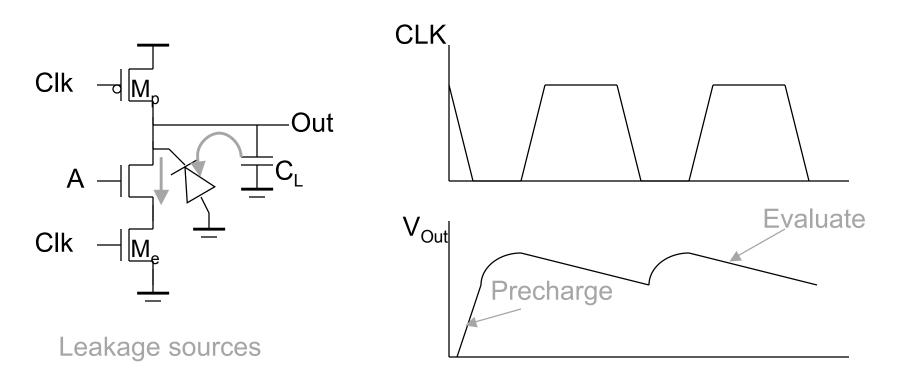

### Issues in Dynamic Design 1: Charge Leakage

#### Dominant component is subthreshold current

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

### Solution to Charge Leakage

Same approach as level restorer for pass-transistor logic

Increase size of inverter to increase capacitance

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

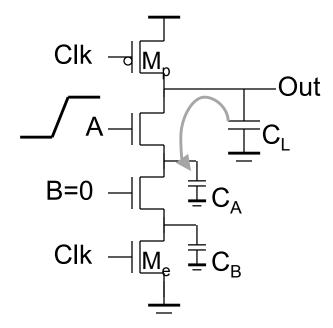

### Issues in Dynamic Design 2: Charge Sharing

Charge stored originally on  $C_L$  is redistributed (shared) over  $C_L$  and  $C_A$  leading to reduced robustness

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

# Dynamic CMOS

Charge Sharing

Assume that the internal capacitances have been dischargedIn the precharge phase, the output capacitance gets charged

•During evaluation, if all the inputs are high except the bottom one, the output capacitance gets distributed to the internal capacitance  $C_{c}$

•The output voltage will drop to  $V_{DD} \frac{C_o}{C_o + 2C_i}$

$\mathsf{C}_{\mathsf{o}}$

•This could be low enough to trigger the inverter, causing a wrong value on the output

CLK

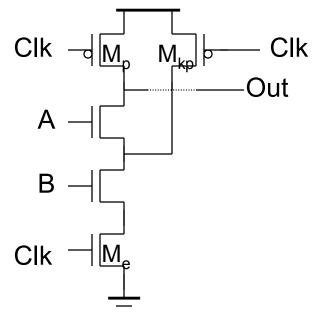

# Solution to Charge Redistribution

Precharge internal nodes using a clock-driven transistor (at the cost of increased area and power)

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

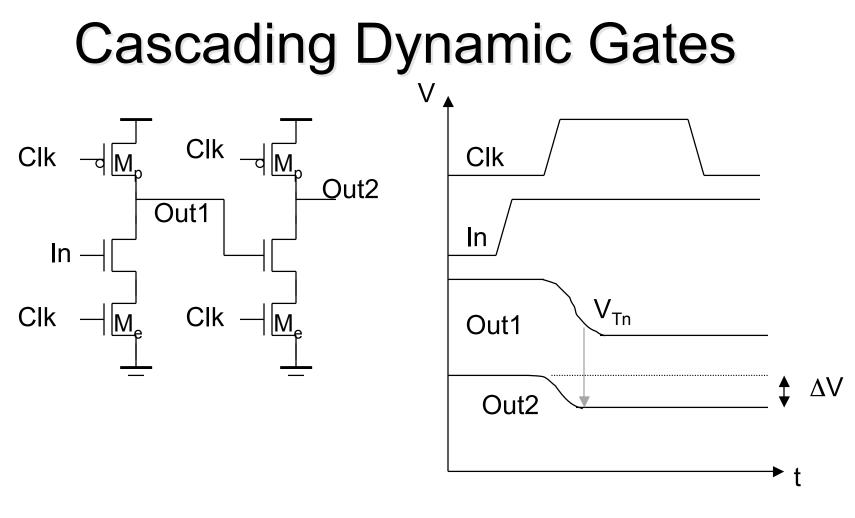

# Dynamic CMOS

Cascade problem

Since the evaluation from the first stage takes some time, the second stage will start evaluating with the precharged input rather than the evaluated input

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

#### Only $0 \rightarrow 1$ transitions allowed at inputs!

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

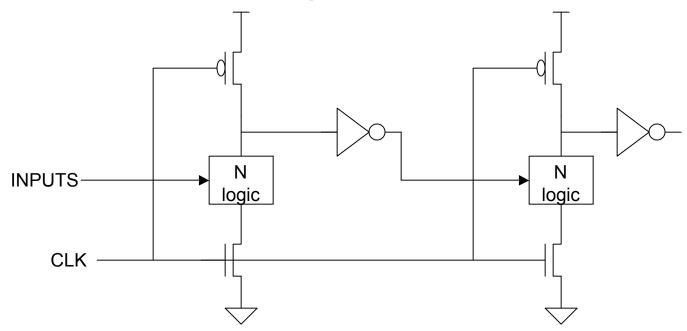

# **Domino Logic**

Solves cascade problem

Since the precharged output from the first stage is 0, it will never activate the pulldown network in the second stage until the first stage evaluation has completed.

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

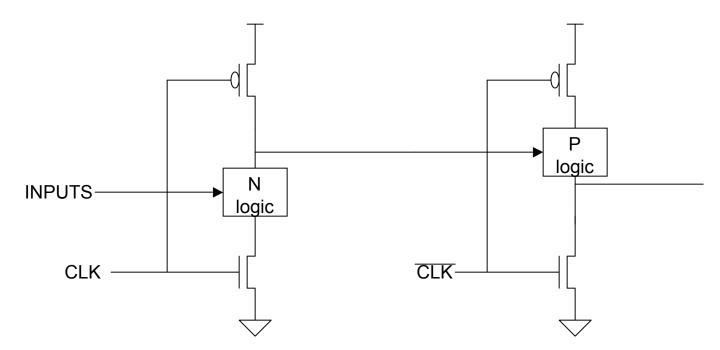

# NP Domino (Zipper) CMOS

Since the second stage is build from p-logic, the precharged output from the first stage will not activate the inputs of the second stage

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

# **Sequential Logic**

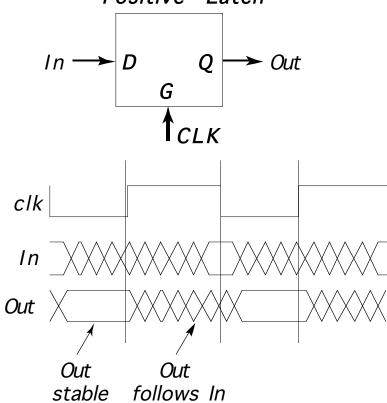

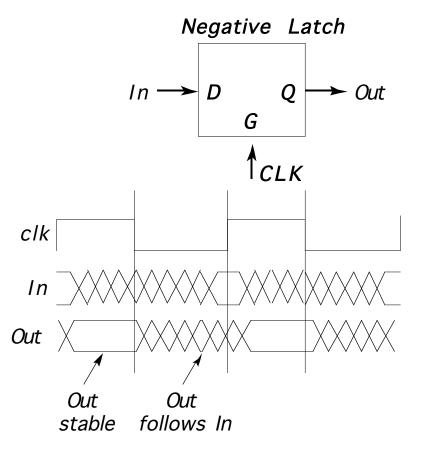

- In our text:

- a latch is level sensitive

- a register is edge-triggered

- a flip-flop is bistable

- There are many different naming conventions

- For instance, many books call edge-triggered registers flip-flops as well

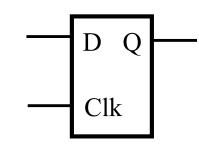

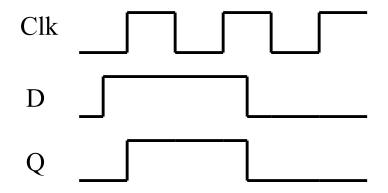

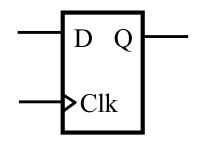

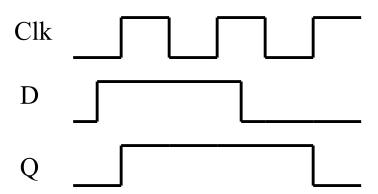

### Latch versus Register

Latch

stores data when clock is low

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14 Register

stores data when clock rises

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

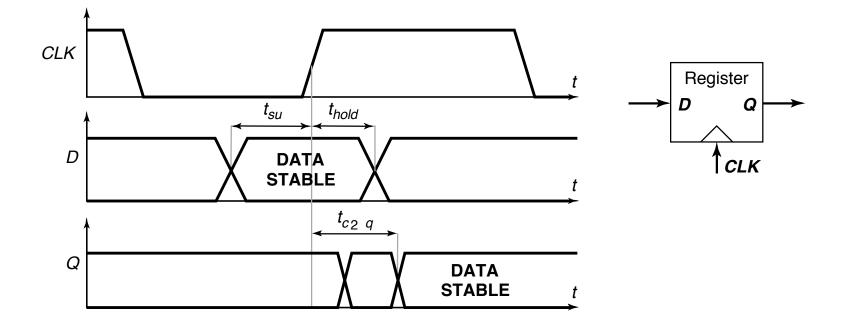

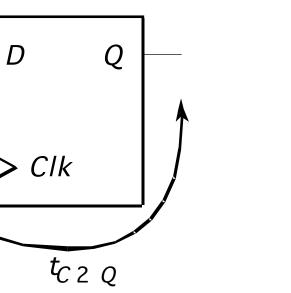

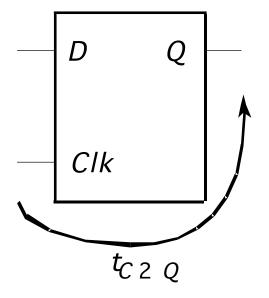

### **Characterizing Timing**

Latch

t<sub>D2Q</sub>

Register

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

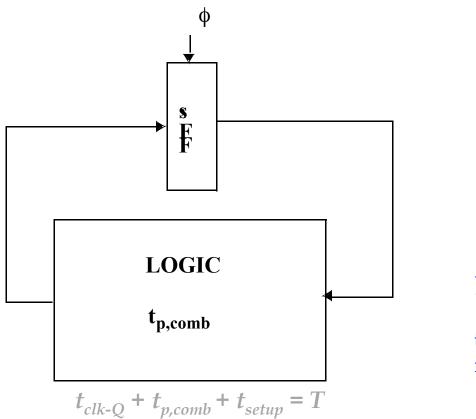

### Maximum Clock Frequency

Also:  $t_{cdreg} + t_{cdlogic} > t_{hold}$

t<sub>cd</sub>: contamination delay = minimum delay

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

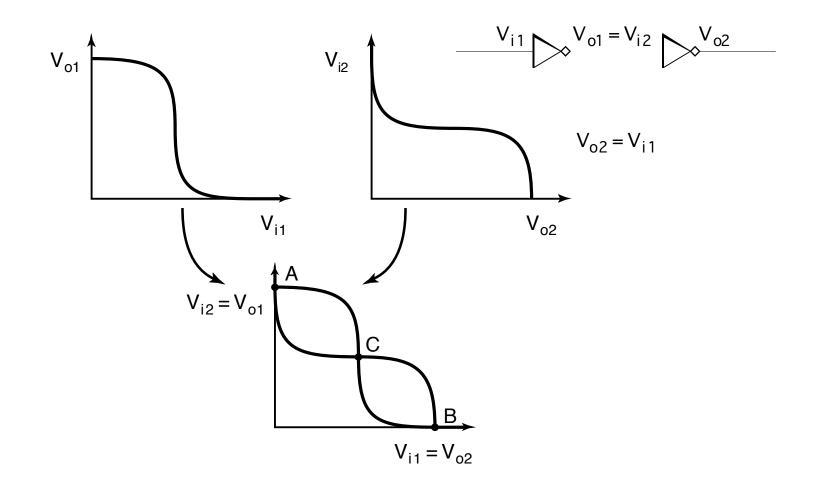

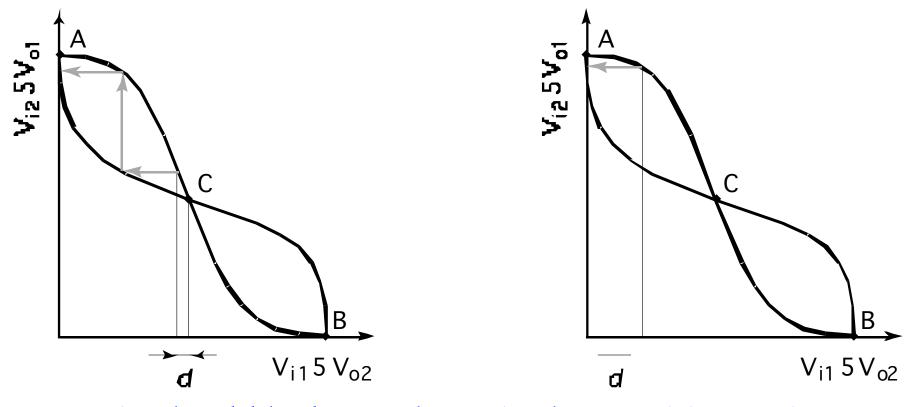

### **Positive Feedback: Bi-Stability**

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

### **Meta-Stability**

Gain should be larger than 1 in the transition region

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

# Writing into a Static Latch

Use the clock as a decoupling signal, that distinguishes between the transparent and opaque states

Converting into a MUX

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

(can implement as NMOS-only)

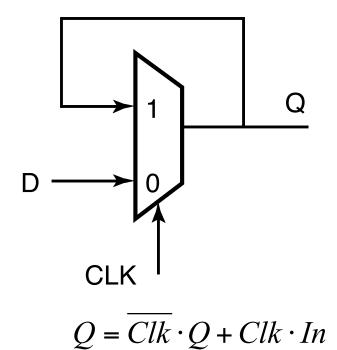

### **Mux-Based Latches**

#### Negative latch (transparent when CLK= 0)

Positive latch (transparent when CLK= 1)

$Q = Clk \cdot Q + Clk \cdot In$

© John A. Chandy Dept. of Electrical and Computer Engineering University of Connecticut

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

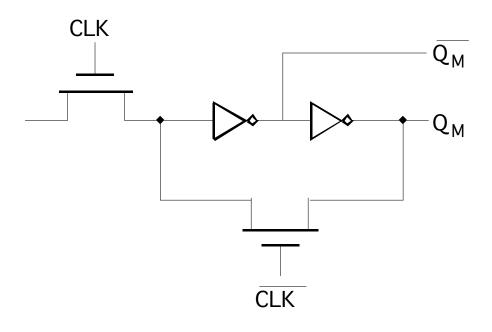

### Mux-Based Latch

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

### Mux-Based Latch

CLK CLK

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14 Non-overlapping clocks

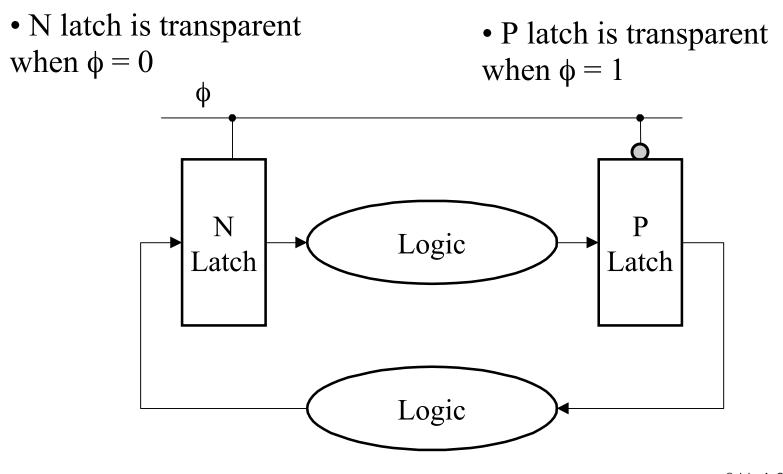

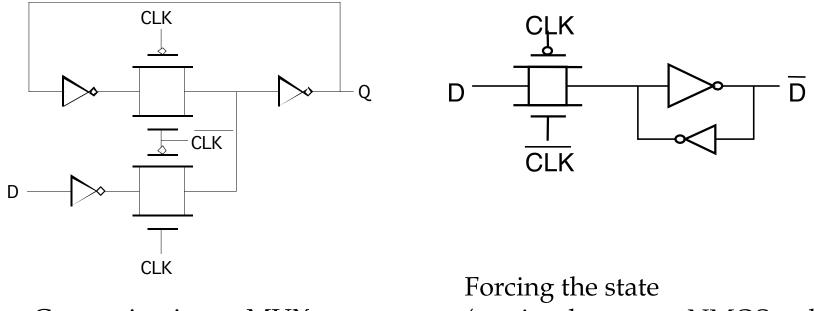

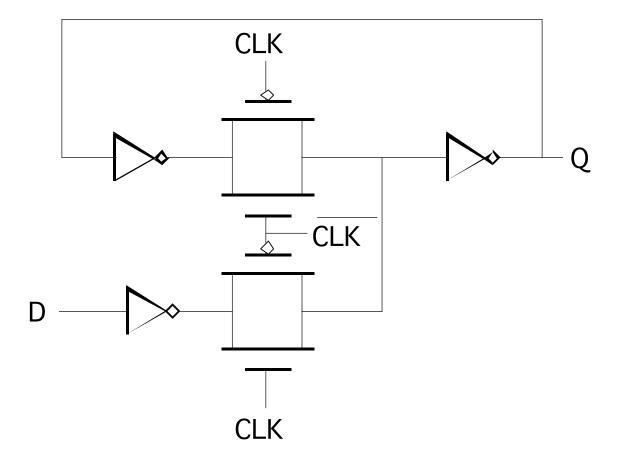

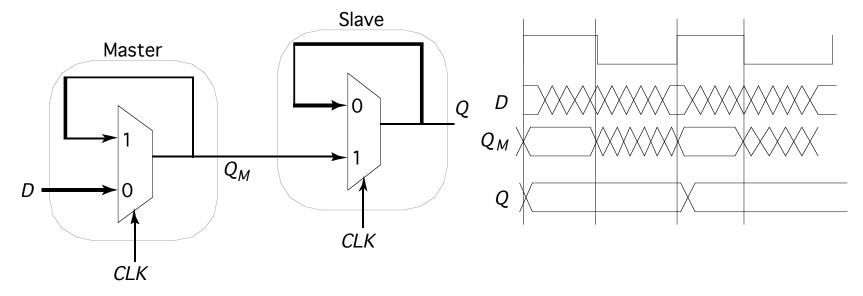

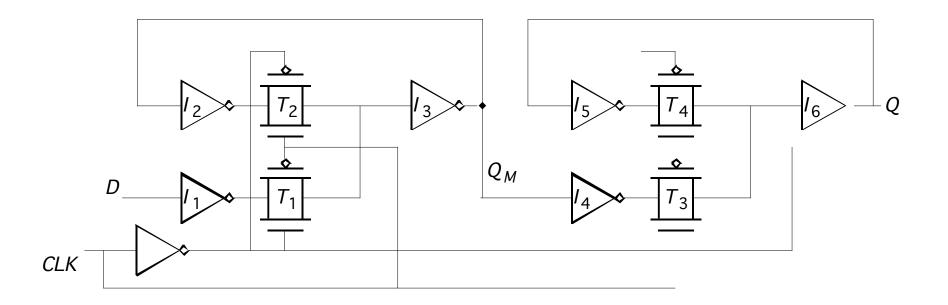

### Master-Slave (Edge-Triggered) Register

#### Two opposite latches trigger on edge Also called master-slave latch pair

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

### **Master-Slave Register**

Multiplexer-based latch pair

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

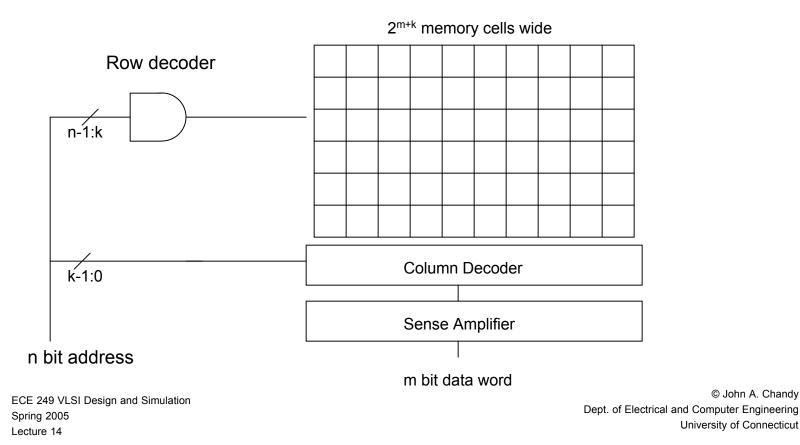

### **Semiconductor Memory Classification**

| <b>Read-Write Memory</b> |                                       | Non-Volatile<br>Read-Write<br>Memory | <b>Read-Only Memory</b>                |

|--------------------------|---------------------------------------|--------------------------------------|----------------------------------------|

| Random<br>Access         | Non-Random<br>Access                  | EPROM<br>E <sup>2</sup> PROM         | Mask-Programmed<br>Programmable (PROM) |

| SRAM<br>DRAM             | FIFO<br>LIFO<br>Shift Register<br>CAM | FLASH                                |                                        |

Random Access Memory

© John A. Chandy

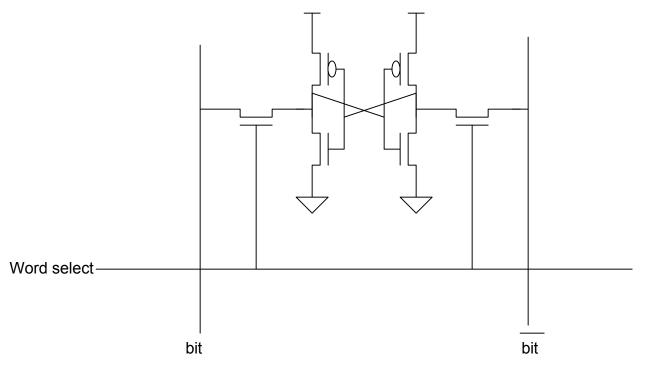

Static RAM Cell

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

- Reads are straightforward

- May need precharge circuitry to pull up bit line

- Writes are trickier

- Use driver transistors that will pull-up or pulldown bit line as necessary

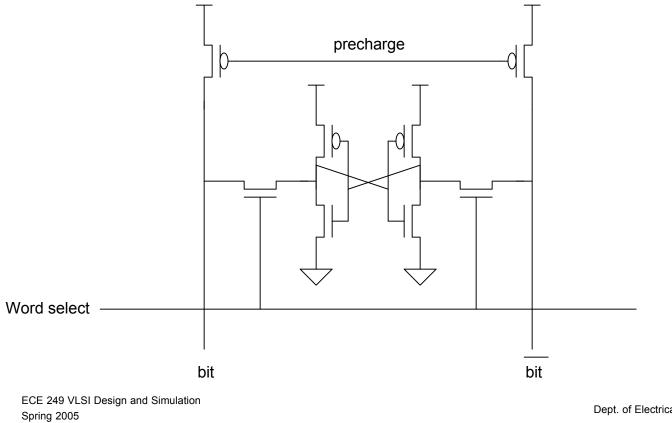

Static RAM Cell with precharge

Lecture 14

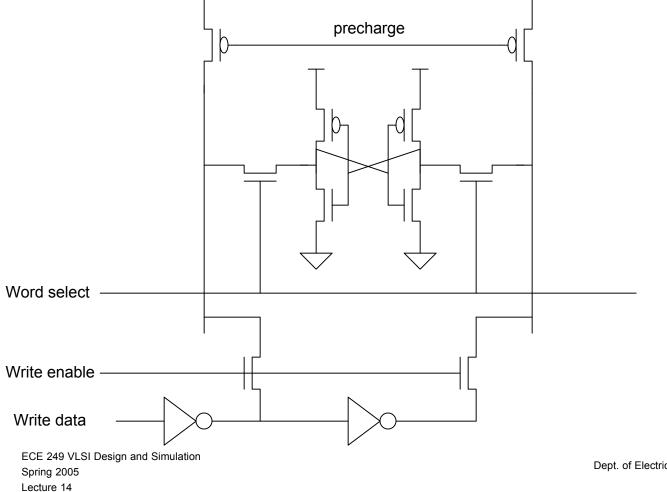

Static RAM Cell write circuitry

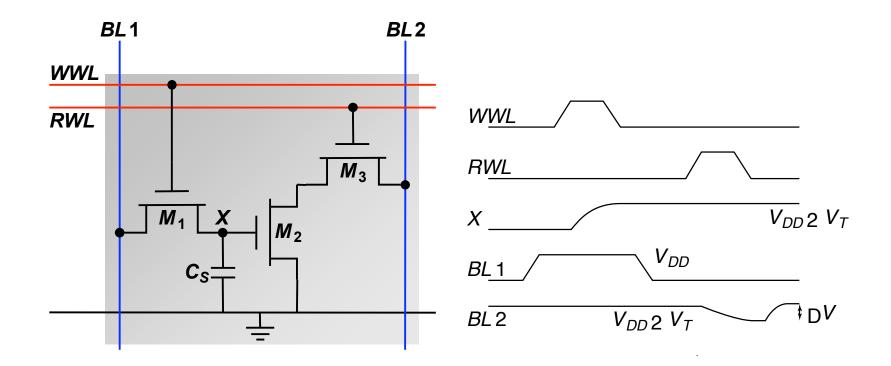

### **3-Transistor DRAM Cell**

No constraints on device ratios Reads are non-destructive Value stored at node X when writing a "1" = V<sub>WWL</sub>-V<sub>Tn</sub>

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

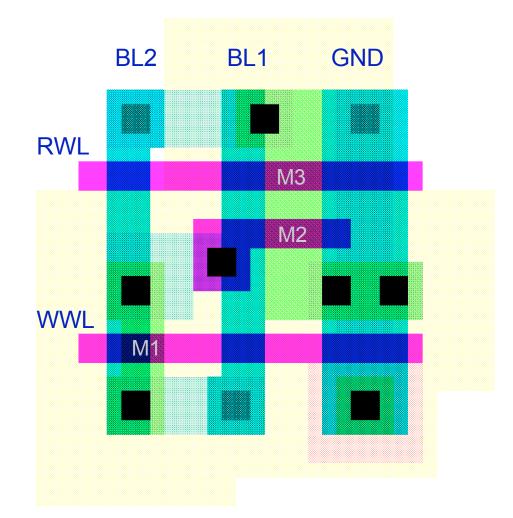

# 3T-DRAM — Layout

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

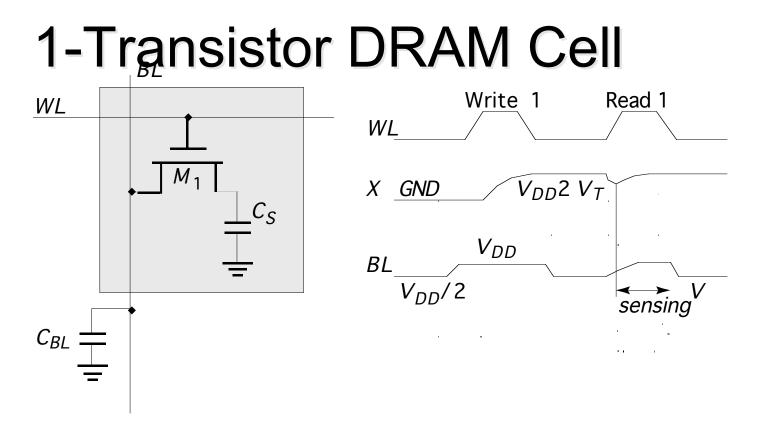

Write: C<sub>S</sub> is charged or discharged by asserting WL and BL. Read: Charge redistribution takes places between bit line and storage capacitance

$$\Delta V = V_{BL} - V_{PRE} = V_{BIT} - V_{PRE} \frac{C_S}{C_S + C_{BL}}$$

#### Voltage swing is small; typically around 250 mV.

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

# **DRAM Cell Observations**

□ 1T DRAM requires a sense amplifier for each bit line, due to charge redistribution read-out.

□ DRAM memory cells are single ended in contrast to SRAM cells.

The read-out of the 1T DRAM cell is destructive; read and refresh operations are necessary for correct operation.

Unlike 3T cell, 1T cell requires presence of an extra capacitance that must be explicitly included in the design.

When writing a "1" into a DRAM cell, a threshold voltage is lost. This charge loss can be circumvented by

bootstrapping the word lines to a higher value than  $V_{DD}$

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

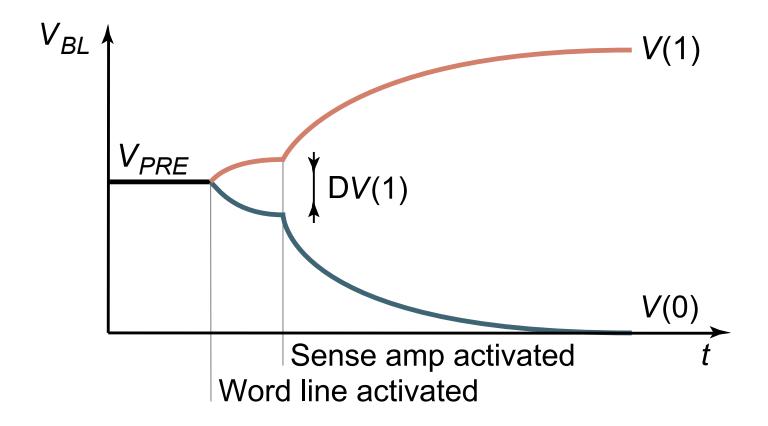

### **Sense Amp Operation**

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

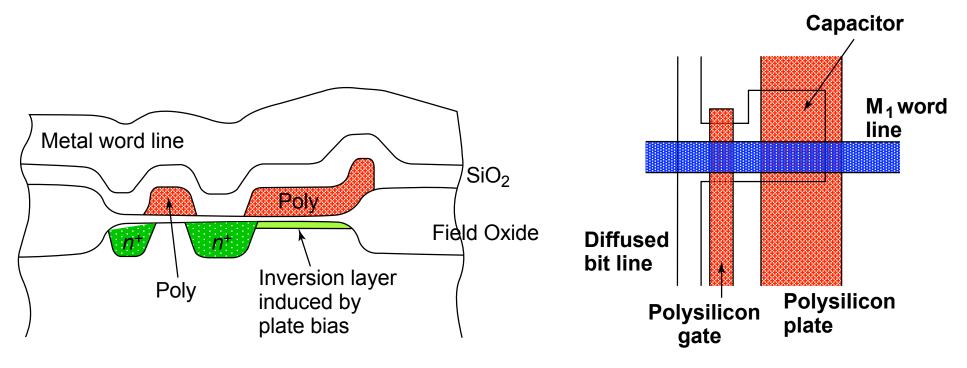

### 1-T DRAM Cell

#### **Cross-section**

Layout

### Uses Polysilicon-Diffusion Capacitance

#### **Expensive in Area**

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

- RAMs

- Static RAM is faster, does not need to be refreshed

- Dynamic RAM is more compact

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14

### Next class

- More about memory

- Control logic

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 14