#### Topics

– Design Strategies

Parts of this lecture were adapted from "Digital Integrated Circuits" Rabaey et al. Copyright 2003 Prentice Hall/Pearson

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

- How do you decide on the composition of the cell library?

- Number of inputs

- Transistor sizing for varying capacitive loads

- Pullup/pulldown ratio

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

#### AA3x

#### AMI5HS 0.5 micron CMOS Standard Cell

#### Description

AA3x is a family of 3- nput gates which perform the logical AND function.

| Logic Symbol | Truth Table |                  |                       |                  |                  |  |

|--------------|-------------|------------------|-----------------------|------------------|------------------|--|

|              |             | A<br>L<br>X<br>H | В<br>Х<br>Ц<br>Х<br>Н | С<br>Х<br>І<br>Н | 0<br>L<br>L<br>F |  |

#### **HDL Syntax**

Verilog .... AA3x *ins(\_name* (G, A, B, C); VHDL ..... ins(\_*name* AA3x port map (Q, A, H, C);

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

#### Pin Loading

| Die Name | Equivalent Loads |      |      |      |  |  |

|----------|------------------|------|------|------|--|--|

| Pin Name | AA31             | AA32 | AA34 | AA36 |  |  |

| A        | 10               | 10   | 2.0  | 2.9  |  |  |

| в        | 10               | 10   | 1.9  | 2.9  |  |  |

| с        | 1.0              | 10   | 1.9  | 2.9  |  |  |

#### Size And Power Characteristics

| Cell | Equivalent Color | Power Characteristics <sup>a</sup>     |                              |  |  |  |

|------|------------------|----------------------------------------|------------------------------|--|--|--|

| Cell | Equivalent Gates | Static $I_{DD}$ (T $_{J}$ = 85°C) (nA) | EQL <sub>psi</sub> (Eq-load) |  |  |  |

| AA31 | 17               | TBD                                    | 3.5                          |  |  |  |

| AA32 | 2.0              | TBD                                    | 4.7                          |  |  |  |

| AA34 | 40               | TBD                                    | 10.0                         |  |  |  |

| AA36 | 5.2              | IH )                                   | 14.5                         |  |  |  |

a. Gee page 2-13 for power equation.

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

#### AA3x

#### AMI5HS 0.5 micron CMOS Standard Cell

#### Propagation Delays (ns)

Conditions: T\_J = 25°C,  $V_{DU}$  = 5.0V, Typical Process

|       |      | Number of Equivalent Los | ads        | 1            | 1            | ß            | 10           | 13 (inax)    |

|-------|------|--------------------------|------------|--------------|--------------|--------------|--------------|--------------|

| Logic | AA31 | <b>T</b> A               | гін<br>гні | 0.20<br>0.28 | 0.33<br>0.36 | 0.43<br>0.48 | 0.65<br>0.63 | 0 64<br>0 73 |

|       | ሰቢ32 | Number of Equivalent Los | ads        | 1            | 6            | 11           | 16           | 22 (max)     |

|       |      | T. O                     |            | 0.29<br>0.29 | 0.39<br>0.42 | 0 48<br>0 52 | 0.55<br>0.61 | 0 63<br>0 71 |

|       | AA34 | Number of Equivalent Los | ads        | 1            | 10           | 20-          | 30           | 40 (max)     |

|       |      |                          |            | 0.31<br>0.24 | 0.37<br>0.35 | 0 44<br>0 47 | 0.50<br>0.57 | 0 56<br>0 64 |

|       | AA36 | Number of Equivalent Los | ads        | 1            | 14           | 29           | 44           | 58 (max)     |

|       |      | 1 ()                     | 1.1.1      | 0.26<br>0.25 | 0.36<br>0.36 | D 44<br>D 44 | 0.51<br>0.53 | 0 57<br>0 61 |

Delay will vary with input conditions. See page 2-15 for interconnect estimates.

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

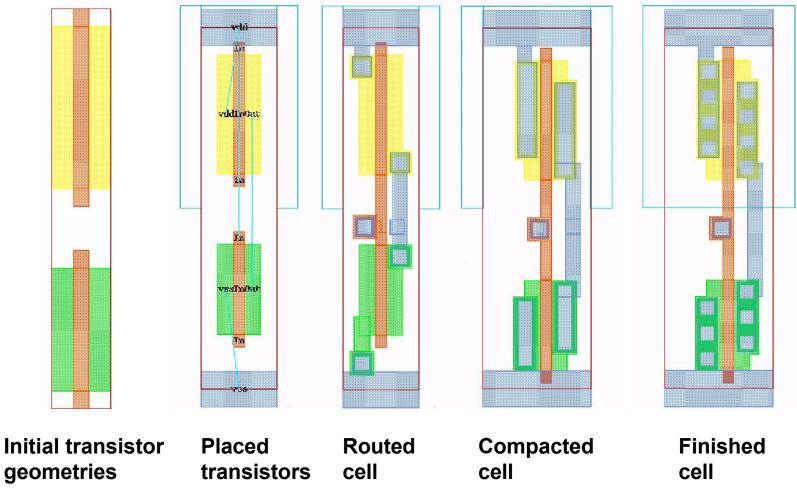

## **Compiled Cells**

- Standard cells

- Must be redesigned for every new process technology

- Design options are limited because of discrete set of cells

- Customized cells would provide more flexibility

- Automatic layout generation for design-specific requirements

#### **Automatic Cell Generation**

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

Courtesy Acadabra

- Hard Macros

- Predetermined physical design

- Fixed transistor and wiring locations

- Dense layout, optimized performance and power characteristics

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

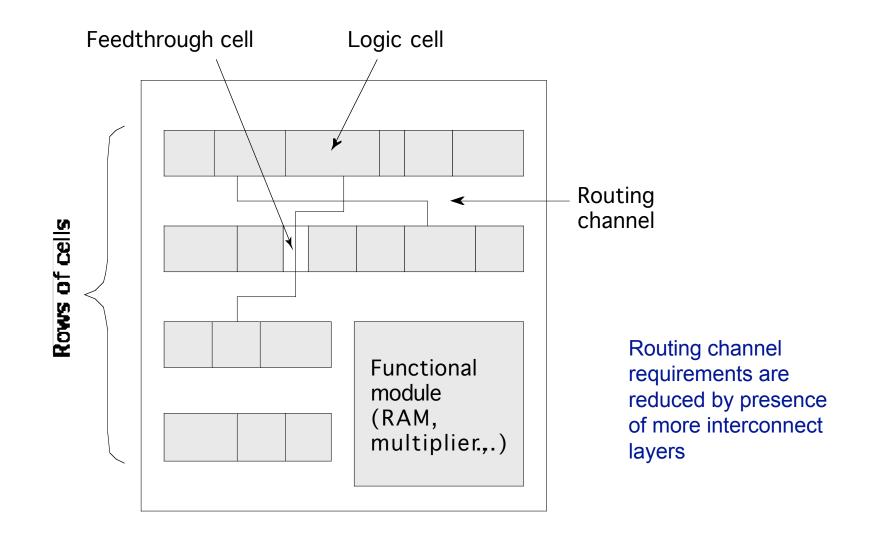

#### Cell-based Design (or standard cells)

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

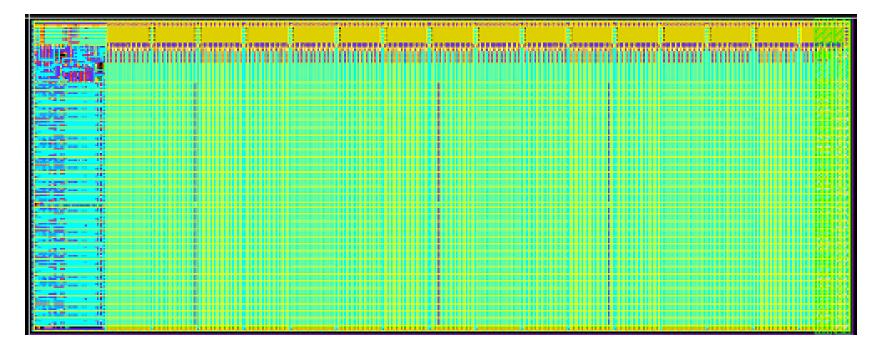

#### 256×32 (or 8192 bit) SRAM Generated by hard-macro module generator

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

- Soft Macros

- Physical design is done automatically

- Easily ported across many different technologies and processes

- Macro cell compiler will take a functional and parameterized description and generate a netlist of standard cells

| <pre>string mat = "booth";</pre> |

|----------------------------------|

| directive (multtype = mat);      |

| output signed [16] Z = A * B;    |

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

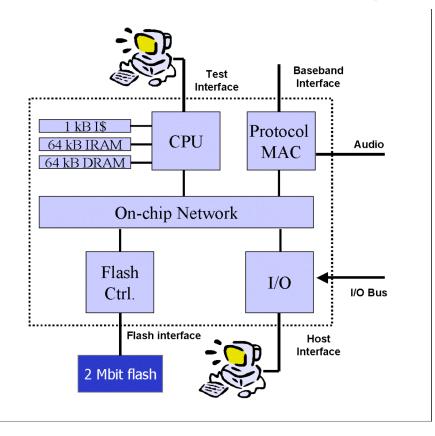

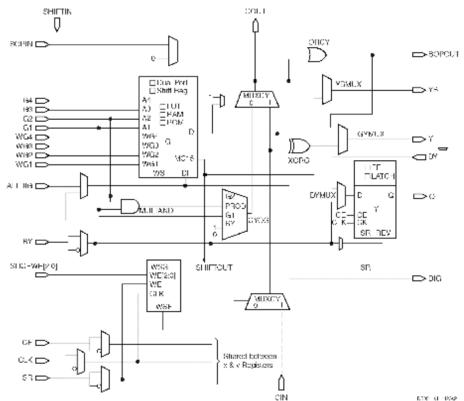

Intellectual property

- Macrocells can be aquired from third-party vendors

- Includes appropriate compilers, debuggers, test vectors, prediction models

- Similar to reusable software libraries

- Examples include embedded processors, bus interfaces, DSP processors, ECC coders, MPEG codecs, etc.

#### "Intellectual Property"

#### A Protocol Processor for Wireless

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

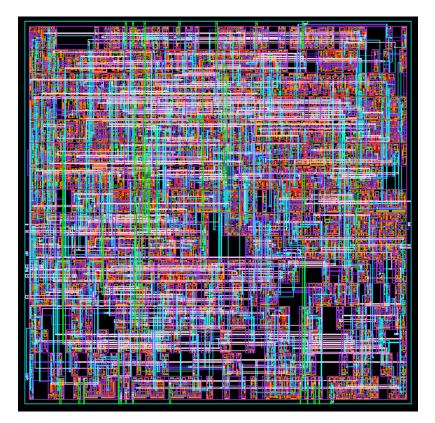

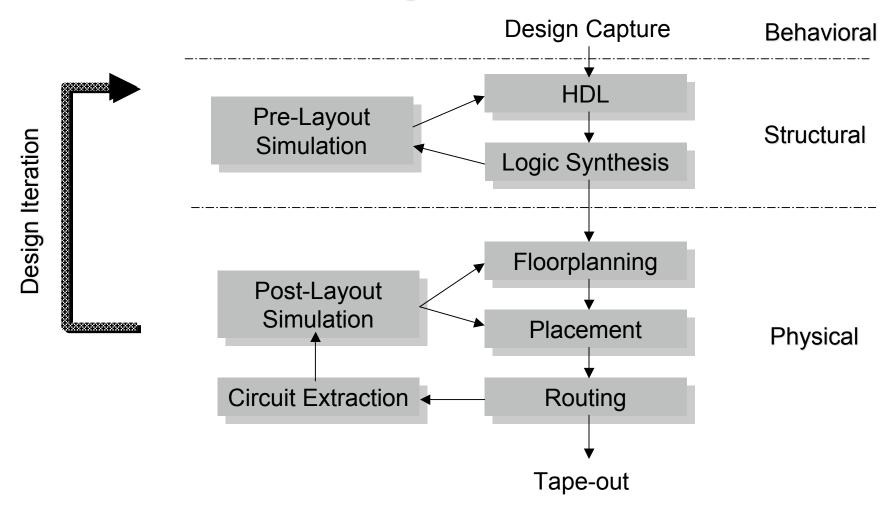

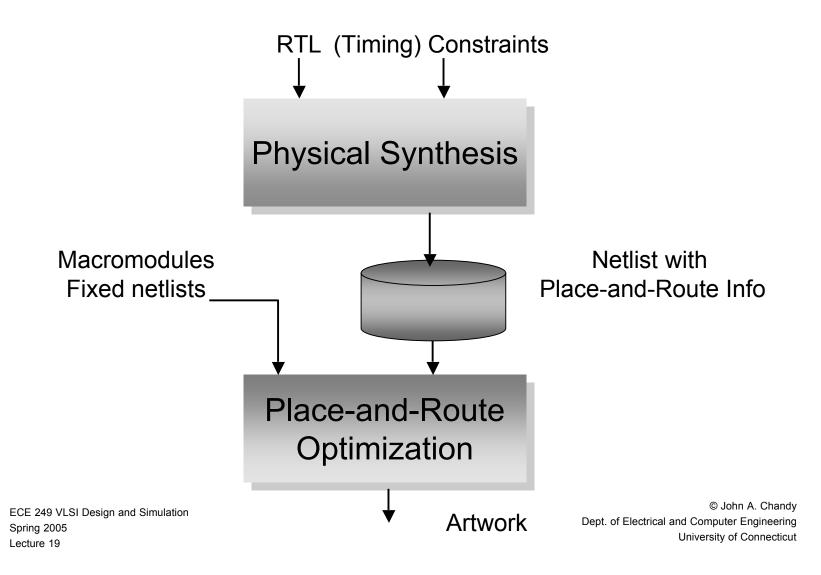

#### Semicustom Design Flow

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

# Integrating Synthesis with Physical Design

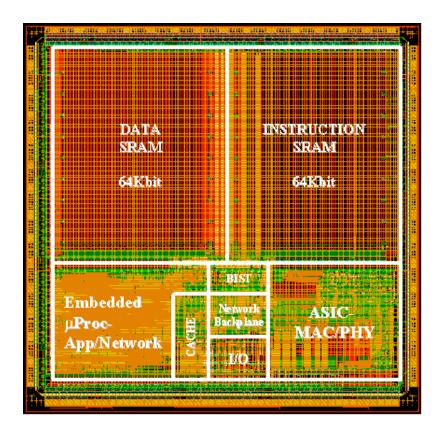

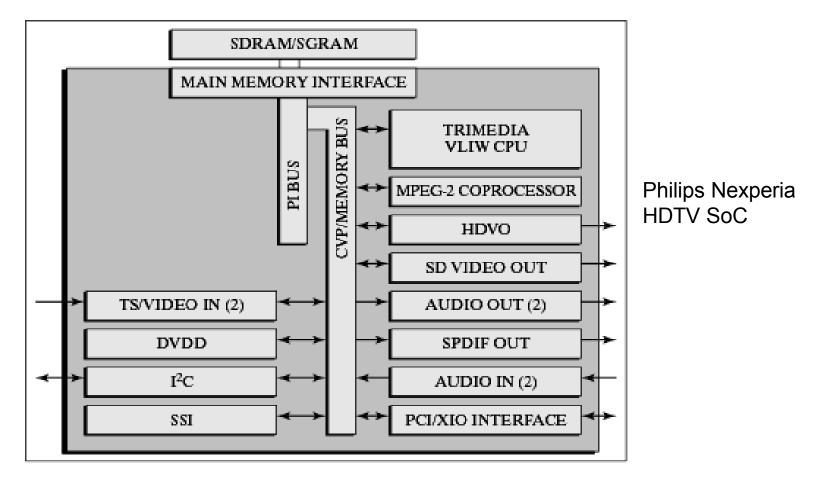

# System-on-a-Chip (SoC) Design

- Embed multiple functionalities on a single chip

- SoC is a natural result of having more and more transistors available

- Managing multiple modules becomes a design challeng

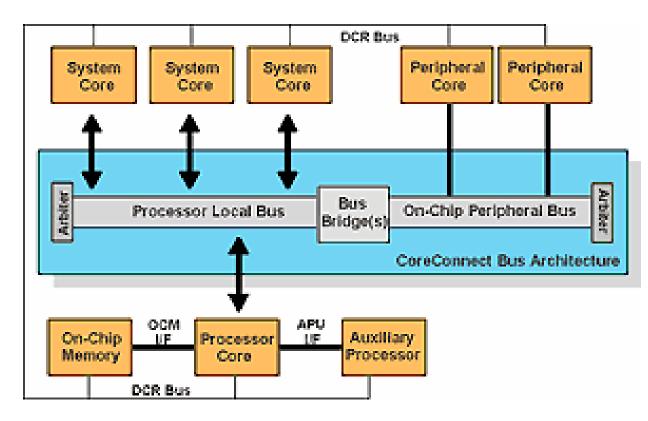

### System-on-a-Chip Design

#### IBM CoreConnect Architecture

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

#### System-on-a-Chip Design

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

# System-on-a-Chip Design

- Embedded applications

- Mixed-mode applications (Analog/Digital)

- Heavy software component

- May have programmable and application specific components

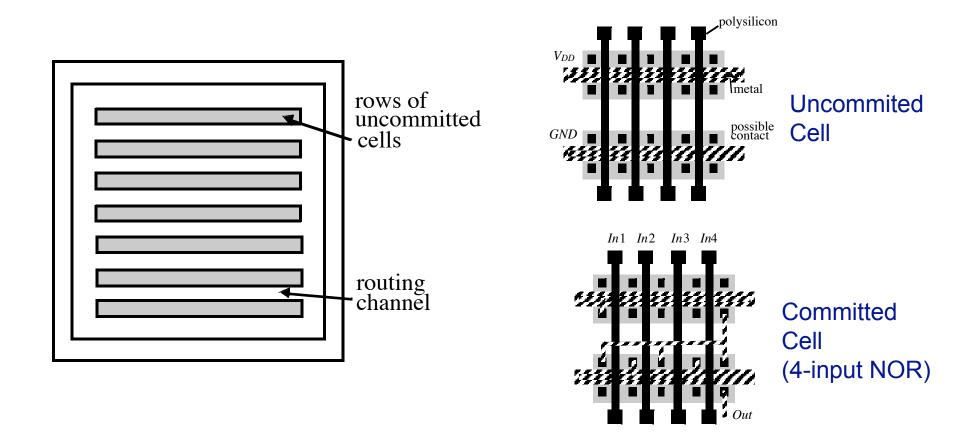

# Array-Based Design

- Cell-based and fully custom designs require a run through the full manufacturing process

- Can take up to several months before the first chip arrives

- Mask generation costs can make it very expensive

- As process technologies get better, the tendency has been to use more and more masks

- Alternative is array-based implementations

# **Array-Based Designs**

- Pre-diffused

- Mask-programmable

- Gate arrays

- Sea of gates

- Pre-wired

- Field programmable gate arrays (FPGA)

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

#### Gate arrays

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

#### Gate arrays

- Less compact than standard cells

- Manufacturing time savings is not as significant because the design times are the most important factor now

- Availability of FPGAs

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

# Field Programmable Gate Arrays

- Prewired arrays

- Programming techniques

- Write-once or fuse-based

- Memory-based

- Non-volatile (Flash, EEPROM, etc.)

- Volatile (RAM)

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

# Field Programmable Gate Arrays

- Programmable Logic Style

- Array-based

- Cell-based

- Function generator

- Look-up table

- Programming Interconnect

- Channel-routing

- Mesh networks

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

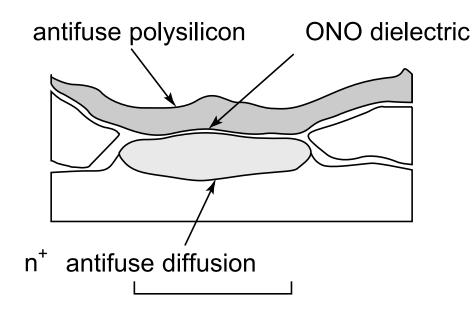

#### **Fuse-based FPGA**

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

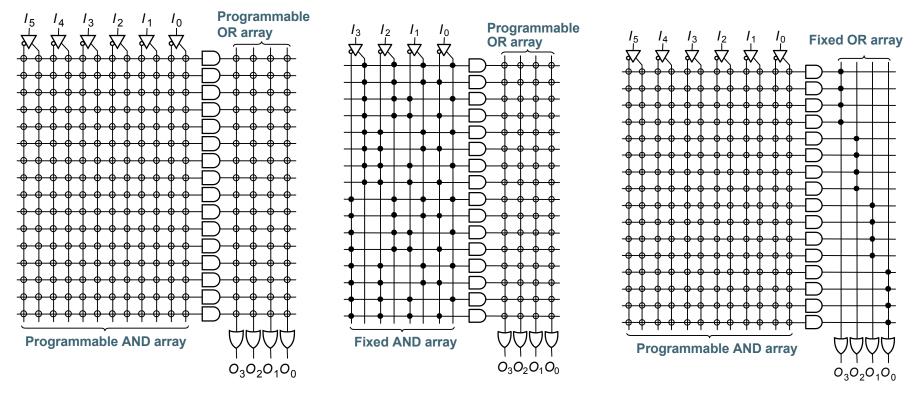

#### **Array-Based Programmable Logic**

PLA

PROM

- + Indicates programmable connection

- + Indicates fixed connection

PAL

© John A. Chandy Dept. of Electrical and Computer Engineering University of Connecticut

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

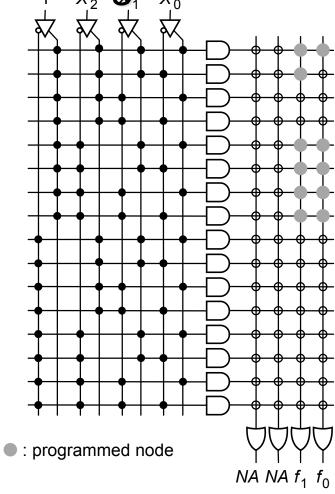

# Array-Based Programmable Logicx.

$$f_0 = x_0 x_1 + x_2$$

$$f_1 = x_0 x_1 x_2 + \overline{x_2} + \overline{x_0} x_1$$

© John A. Chandy Dept. of Electrical and Computer Engineering University of Connecticut

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

## Array-Based Programmable Logic

- Lower density than custom

- All minterms may not be actively used

- OK if you have large fanin

- Lower performance

- Each node has significant capacitance

- Only implements combinational logic no registers or flip-flops

### Array-Based Programmable Logic

Macrocell-based PAL

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

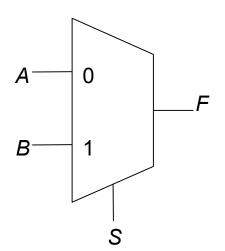

#### **Cell-based Programmable logic**

• Multiplexor as a function generator

| Con |   |   |                |

|-----|---|---|----------------|

| Α   | В | S | <b>F</b> =     |

| 0   | 0 | 0 | 0              |

| 0   | Х | 1 | X              |

| 0   | Y | 1 | Y              |

| 0   | Y | X | XY             |

| X   | 0 | Y | XY             |

| Y   | 0 | X | XΥ             |

| Y   | 1 | X | X + Y          |

| 1   | 0 | X | $\overline{X}$ |

| 1   | 0 | Y | Ϋ́             |

| 1   | 1 | 1 | 1              |

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

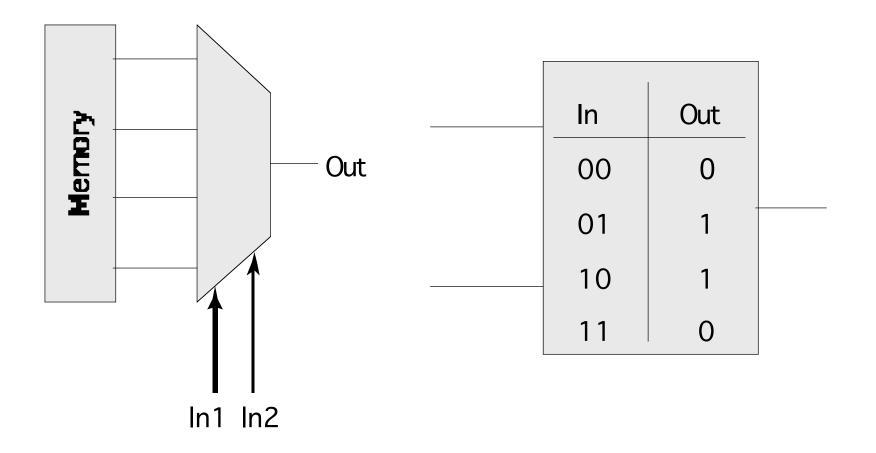

### Lookup Table

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

#### Lookup Table

Configurable Logic Block (CLB) - Xilinx

Virtex II

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

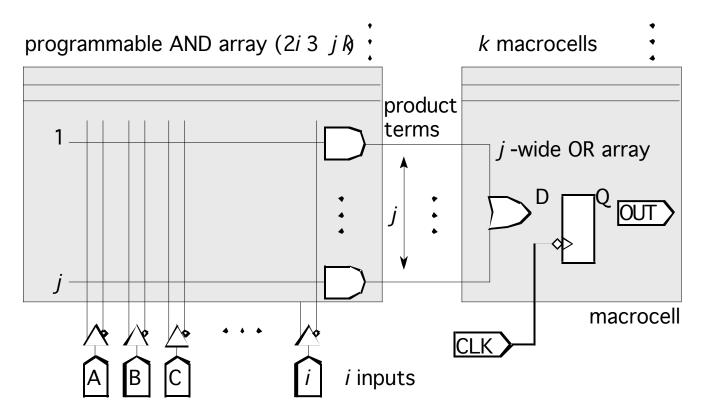

### **Array-based Programmable Wiring**

Lecture 19

### Array-based Programmable wiring

- Transistor method takes more space

- Use Fuse or antifuse methods

- Write-once can not change

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

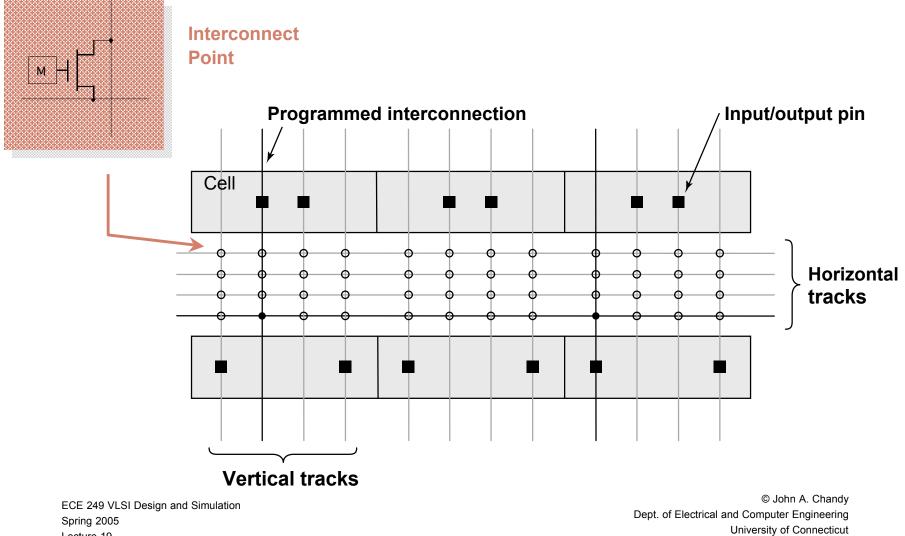

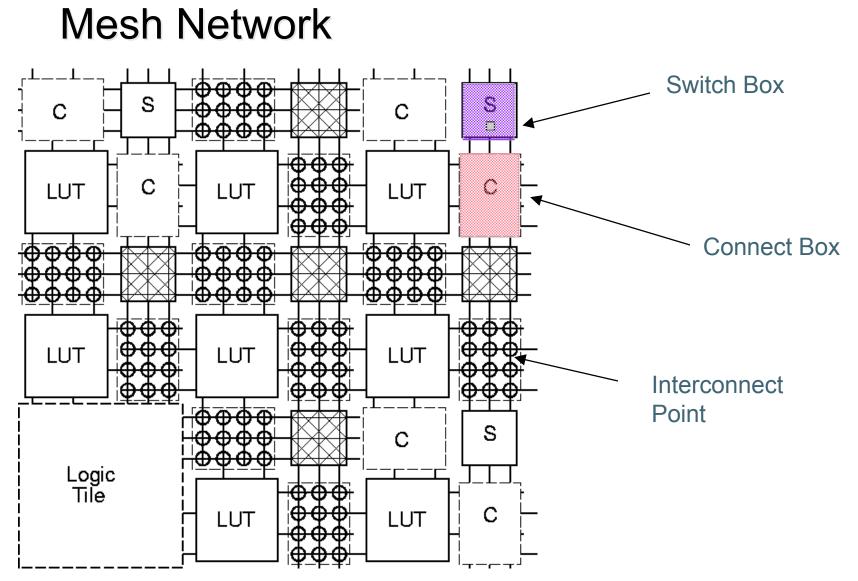

#### Mesh Network

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19

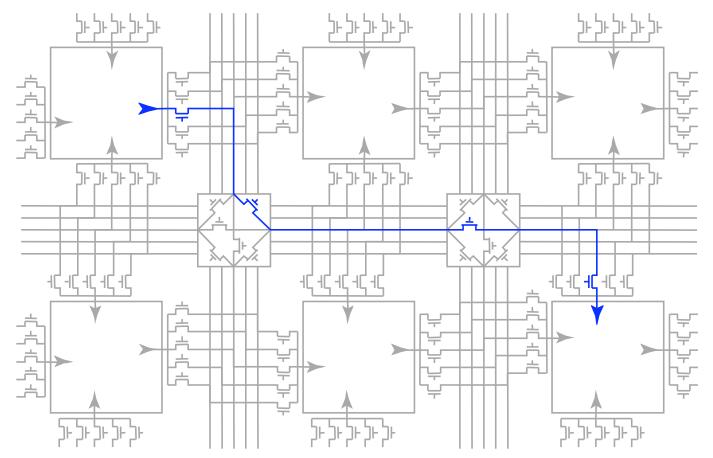

### Mesh Network

- Sometimes can not route interconnect

- Pass transistor has a voltage drop

- RAM based progammable switch matrix

- Good for local wiring

- Global wiring will have large capacitive loads

#### Next class

- Testing and verification

- Exam 2 next Thursday

ECE 249 VLSI Design and Simulation Spring 2005 Lecture 19